身为资深硬件工程师,我在DDR4内存时序问题上拥有深厚的认知与实践经验。所谓的DDR4内存时序,即数据在内存模块内进行传输的精准时间顺序,决定了其稳定性及整体性能表现。本篇文章主要围绕DDR4内存时序展开深入剖析,包括了解什么是内存时序、关注时间参数的原因、怎样解读这些参数,以及时序调整对于系统运行效率的重要性等诸多内容。

什么是DDR4内存时序?

DDR4内存时序用以描述信息传输时,各模块信号的相对时间间隔及其长度。CPU与记忆体讯息互换主要由总线负责执行,而它们在总线上的抵达及维持时间须严格遵循特定规则——DDR4内存时序。其中,这一套规则包含诸多参数,譬如CL(CAS Latency)、tRCD(RAS to CAS Delay)以及tRP(Row Precharge Time)等。

尽管DDR4内存较DDR3在速度、存储容量及能耗表现上有所突破,但其高频率却对时序提出更严苛要求。因此,适当调节完善DDR4内存时序对其性能提升非常关键。

为什么需要关注时序参数?

时序设定对内存模块的稳定性及表现至关重要,不当设置会引发数据传输错误,甚至系统崩溃等严重问题。正确理解并调整DDR4内存的时序参数,有助于保障设备平稳运行,充分释放硬件潜能。

近期,技术的飞速演变使得DRAM芯片迭代加速;新一代芯片通常拥有更高的运行速度与更短的响应时间。适时调整时序规格有望最大化新型硬件所激发的性能优势。

如何理解内存时序参数?

首先明确每个时序参数的具体作用及其在系统性能中的地位。如“CL”(CLock Swift),这一参数反映从列地址选定至可使用输出数据所需的周期数。数值越低表示数据传输速率越高。

在探讨超快充电技术时,除电容性负载(CL)之外,还需深入理解其他关键参数如延迟时间容忍度(tRCD)、延迟时间(tRP)及转换速度(tWR)等。唯有透彻了解各参数间的内在联系及其影响,方能进行精准且合理的调节。

实际工作中,必须根据特定硬件平台与应用环境进行参数调优。各厂商间主板、CPU对内存频率及延迟支持存在差异,务必慎重选择最优配置以确保系统稳定运行。

时序调整对系统性能的影响

精确设定DDR4内存的时序能表现出明显的性能提升效果。首先,降低同等频率下的延迟有助于增强数据读取和写入的速度,进而提升系统响应水平;其次,在进行超频操作时,适宜地增加延迟可提升系统稳定性,规避由于过高频率引起的不稳甚至崩溃状况。

除此之外,精心设定DDR4内存时序亦有助于节能降耗。精细调节各参数使功率保持优秀且不牺牲性能,以此实现能源节省及散热负担减轻的双重效益。

如何优化DDR4内存时序?

在优化DDR4内存时序以前,须明确自身设备认可的最优设置范围。查阅相关资料如主板、CPU说明书或官网中的频率、延迟权限等关键数据。

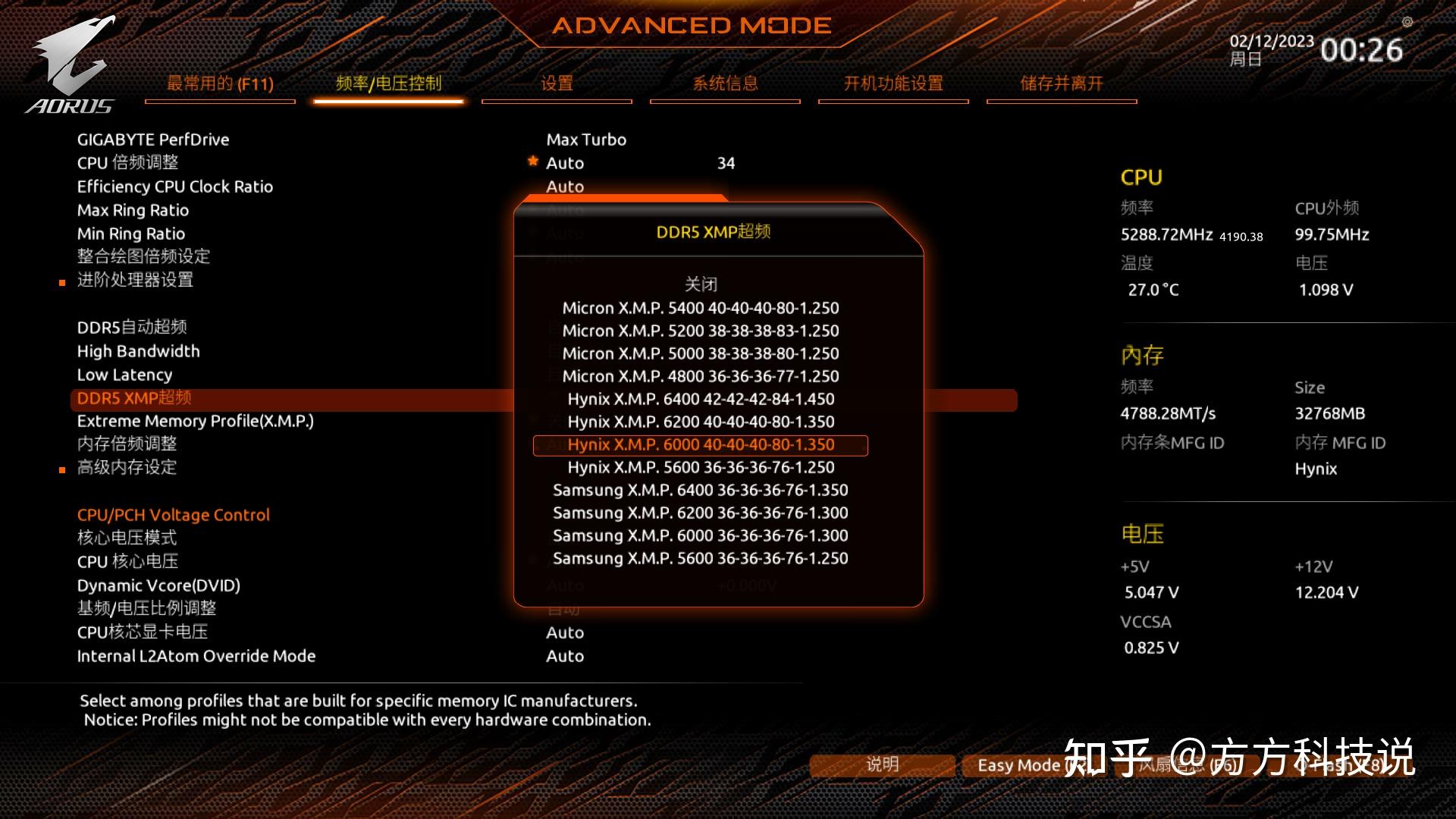

接下来,在 BIOS 设定界面对各项参数进行细致调整,并进行稳定度测试。依据测试结果逐步修正每个参数值,同时关注各参数间潜在的影响关系。

在此优化过程当中,务必确保对重要数据的妥善备份及充分风险评估。若不当或者过于激进的调整操作有可能引发系统停机甚至数据遗失等严重后果。

结合实际案例分析

实例诠释DDR4内存时序优化的重大意义。某客户在超频过程中遭遇频繁死机问题,细查原因为DDR4内存不合理配置所致。专业人员针对性地调整了内存时序参数(降低CL调至12;适度增大tRCD与tRP值),使之成为稳定可靠的系统,显著提高性能表现。

本案例明确显示,准确认知和调节DDR4内存时序对解决此类难题至关重要,会取得显著成效。