DDR3内存简介

DDR3内存属常用计算机内存,因其迅速传输速率及极低能源消耗而盛行。该内存利用双倍数据传输率技术,较之早期的DDR2内存,性能卓越显著。于电子系统之内,DDR3内存起着决定性作用,直接影响到系统速度以及稳定程度。重点探讨DDR3内存地址相关内容。

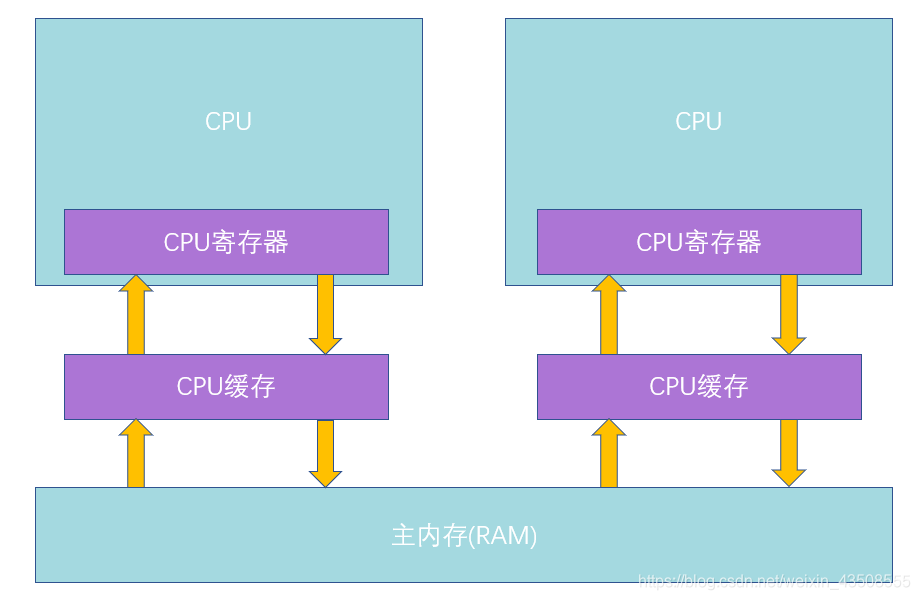

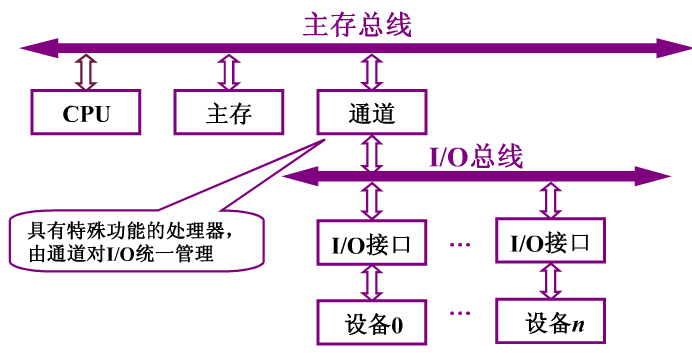

地址总线与数据总线

计算机系统中的核心概念包括地址总线与数据总线。其中,地址总线承载着CPU产生的内存地址信息,而数据总线则用以实现CPU与内存间的数据交换。直译3代(DDR3)内存通过地址总线定位并访问存储区的特定数据。为实现这一目的,CPU先向DDR3内存传递指定地址信息,再以便读取或写入数据操作。因此,充分理解DDR3内存地址框架及工作机制对理解整个计算机系统的运行至关重要。

DDR3内存寻址方式

DDR3 DRAM运用了双倍数据传输速率技术,与之前的型号相比,其寻址方式有所差异。它为每颗芯片指定唯一地址,以便中央处理器能根据该地址准确地找到所需数据。DDR3的寻址方式由行地址和列地址两大部分组成,CPU首先传送行地址至内存以定位待读取数据所在的行,接下来发出列地址,以确定确切的数据位置。此种寻址方法显著提升了数据载入速度及整体系统效能。

DDR3寻址范围

DDR3内存的寻址能力同样有其局限性。单个DDR3芯片最大可寻址范围由其物理构造和制造成本所限。然而,通过组建具备多芯片通道的内存条,整体系统就能大幅提高对内存空间的有效利用。因此,在设计计算机系统时,对于DDR3内存的搭建和设置需依据系统对高速大容量数据处理需求进行科学决策。

DDR3寻址模式

在行列地址寻址基础上,DDR3提供多元的寻址模式支持,如自动预充(APC)及自动刷新的功能(AR)等。丰富多彩的寻址模,有助于提升体系效能、降低能耗效率,保障数据传输稳定性与可靠性。此种寻址方式对计算机系统的性能优化和硬件设备的长久使用发挥了关键作用。

DDR3地址信号排布

事实上,在实践应用中,优化DRAM3地址信令布局至关重要。优良的信令分布有助于减小相互干扰、提高数据传输的精度以及降低系统噪音的水平。创新性地调整PCB板上DRAM3内存芯片引脚接口布局,能够显著减少信令之间的串扰和交叉耦合,进而大幅提升整个系统的性能表现。

DDR3频率与地址延迟

DDR3内存的实际运用环节,频率与地址延迟成为制约其性能发挥的关键要素。由于高频率有助于提高数据处理速率,然而也将加剧能耗压力,而地址延迟则直接决定CPU对DDR3内容读取所需时长。因而在挑选DDR3内存时,必须权衡频率和延迟之间的取舍,以求在满足性能需求的前提下最大程度地降低能耗。

DDR4与未来发展

随着科技的飞速发展,DDR4内存已逐步取代DDR3内存成为市场主导。相较前者,DDR4内存拥有更宽敞的带宽、更高的运行速度及更低的能耗。展望未来,随着技术的进一步深化,更高版本的DDR内存产品将面世,以应对日益增长的运算需求。