DDR3匹配电阻即为DDR3存储器模组中用以调节信号线上特性阻抗以实现稳定信号传输的关键元件。DDR3内存模块中,匹配电阻对于减少信号反射和串扰至关重要,能够提升数据通信的可靠性及稳定性。其选型与布置对模块整体性能具有深远影响,故而深入理解匹配电阻的工作原理及运用范畴至关重要。

为确保DDR3内存模块内各类线路与主板控制器间的信号传输品质,须配置相应匹配电阻进行调节。经过科学选用及精准布设匹配电阻,可大幅减少信号传递过程中的反射及串扰状况,进而提升系统运行效能。

DDR3匹配电阻的原理

DDR3适配电阻原理主要关注信号传输线上的阻抗匹配。DDR3内存模组中的数据线及地址线等皆为微带线或差分支流线,特性阻抗多设定为50欧姆,同样,主板控制器之特性阻抗亦设定为此标准。为确保信号传输过程无反射或串扰,需对信号源端(内存模组)及终点(控制器)间特性阻抗进行细致配比。

为确保信号传输做到最佳质量,应根据信号路径两端所需阻抗来合理设置匹配电阻,以达到满足特性阻抗的效果。若未配置或选配不好,便会引发如信号反射、噪声干扰等问题,直接关系到整个系统的稳定运行和效能发挥。

DDR3匹配电阻的选取

在选择DDR3匹配电阻时,需要考虑以下几个方面:

阻抗值的设定:依据内存模组与控制芯片间的特制阻抗来计算匹配电阻的数值。通常情况下,标准的DDR3内存模组及主板控制芯片均以50欧姆作为标准特征阻抗值进行设计配置。

容差:匹配电阻的容差不容忽视,其大小关系到信号传输质量。过大的容差可能导致实测阻值偏离设汁值甚远。

功耗承受:鉴于DDR3存储器工作过程中产生的功耗,应重视所选配套电阻的功耗承载力。

封装选取:依照具体运用需求挑选适宜的封装形式匹配电阻。

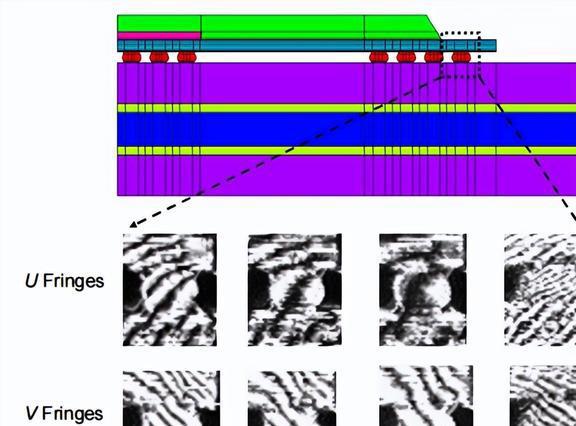

DDR3匹配电阻的布局

优良的布局方案对DDR3匹配电阻起着不可或缺的作用。科学的布局方式能够缩小信号传输距离,有效削弱串扰与回流影响,从而提升系统整体稳定性与可靠性。

求简对称:尽减接口间的导线及寻址线路长度,力求布局周全对称美观。

控制串扰:力求正确排列各种传输线,规避相互之间的干扰。

3.地域分离:将地域分离开来有助于降低地回流问题。

4.远离高频干扰源:避免将匹配电阻布置在高频干扰源附近。

注重散热:科学的布局可助于散热,高效地降低高温环境下的功耗和温升。

如何验证DDR3匹配电阻效果

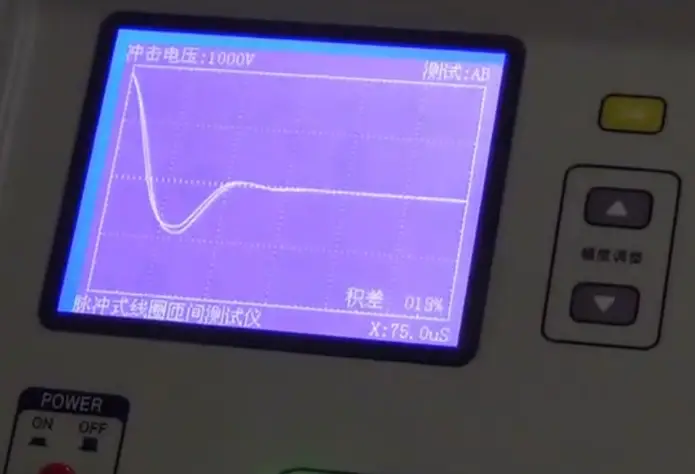

要检验DDR3匹配电阻的功效,常需依赖示波器此类测试器械进行精准测量。其操作过程如下所述:

对接示波器:将示波器对应接口与需验证运作的设备信号传输线(如数据线、地址线等)紧密相连,启动示波器进行观测。

传送试验数据:通过主设备将测试数据传送至内存模块中,同时密切关注波形在示波器的演变情况。

察看波形:确保波形平稳无显著畸变或震动。

参数调优:依据测验数据,对匹配电阻值或布置方案做出相应调整,确认无误后重复试验。

常见问题及解决方法

在运用DDR3内存模组过程中,常面临与匹配电阻有关的常见困惑。

装配不当:倘若组装不妥,或者连接出错,都易使信号稳定性受损甚至功能发挥受阻。

选型失当:误用数值或容差不当,均可引发系统运行问题。

3.布局不当:布局不当会增加串扰干扰、地回流问题等。

针对这些问题可以采取以下解决方法:

1.仔细查看安装手册并按照规范安装;

2.核对选型参数并确保符合要求;

3.优化布局设计并重新验证效果。

结语

本篇文章深入剖析了DDR3匹配电阻的相关知识,包括其工作原理,选择标准,设计布局及验证手段。实际应用方面,精确选用与配置DDR3匹配电阻对提升系统稳健性与性能有着举足轻重的地位。期望此文能为广大读者深度理解并运用DDR3内存模块中的匹配科技提供支持。