DDR3电路设计的重要性

随着当今信息科技高速发展,消费者对电子产品的性能与稳定性有着极高要求。DDR3作为主流内存格式,其电路构造关乎设备运作速率及数据处理效能。探究DDR3电路设计原理,对于提高产品品质与用户体验起到关键作用。

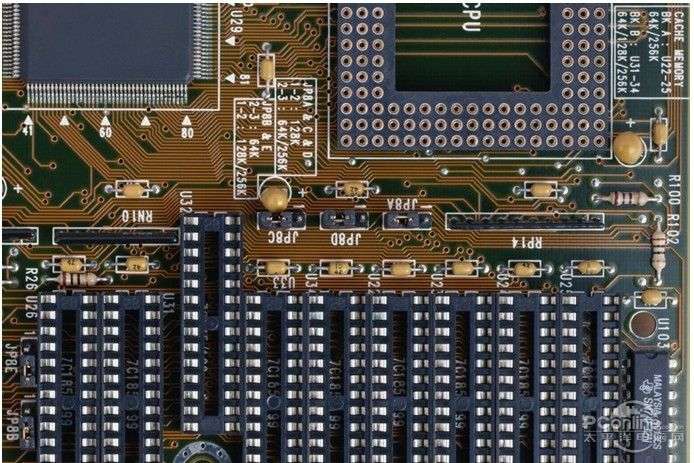

在DDR3电路设计过程中,需充分考虑多重因素,如时序限制、布线路径规划、保证信号完整性以及功耗控制等方面。尤其在时序设计环节,它至关重要。DDR3内存在严格的时序需求,如时钟频率、延迟以及数据传输速率等方面均有明确规范。唯有通过精确设计电路,方能确保数据传输的稳定及准确性。

DDR3电路设计中,布线规划尤为关键,它可缩短信号传输路径,改善延迟现象,提升系统功能。与此同时,良好的布线亦有助于减少信号干扰及地回流问题,保障信号的完整稳定。

DDR3电路设计中的信号完整性

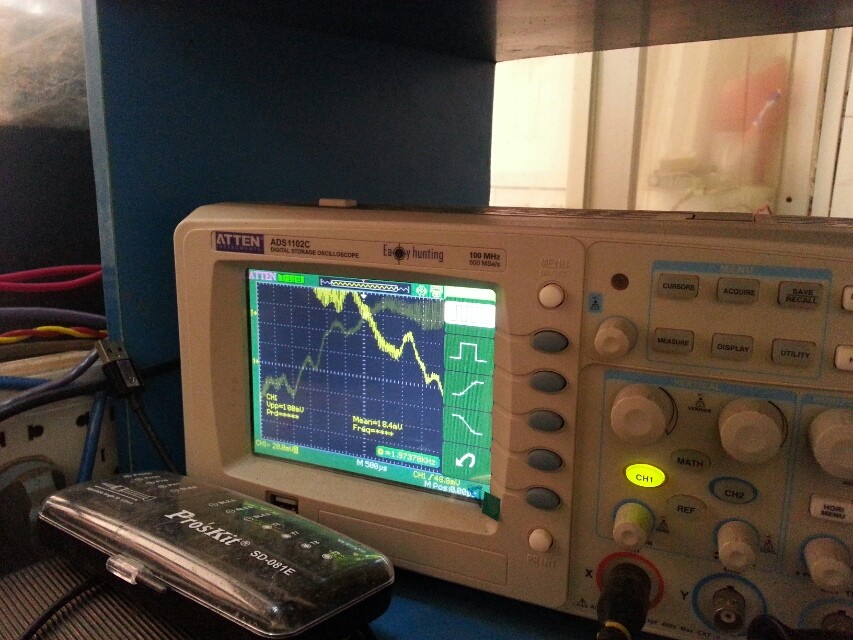

在 DDR3 系统设计环节中,确保信号完整性乃核心要素之一。所谓信号完整性,即保证信号波形传递过程中的无损,防止抖动及谐波失真的发生。鉴于 DDR3 内存工作在较高频段与高速率下,这类问题尤须重视。

为保障 DDR3 电路设计的信号完整性,首要任务便是面对地回流与供电回流所带来的挑战。地回流是使接地端口拥有较低阻抗路径,以便达成充分流畅的地回路,借此降低信号噪音;至于供电回流,其初衷在于减少供电引脚之间可能产生的串扰。

在DDR3电路设计过程中,必须关注阻抗匹配以及终端匹配的处理,这样才能有效减少反射提高信号品质;同时,终端匹配有助于降低回波和干扰,进而增强系统的稳定性。

功耗控制在DDR3电路设计中的应用

节能降耗被视为现代科技产品设计中至关重要的要素,特别是在DDR3电路设计环节。面对日益增长的能耗需求,如移动设备及云计算技术,如何精准有效地降低能耗成为了DDR3电路设计师们的重大课题。

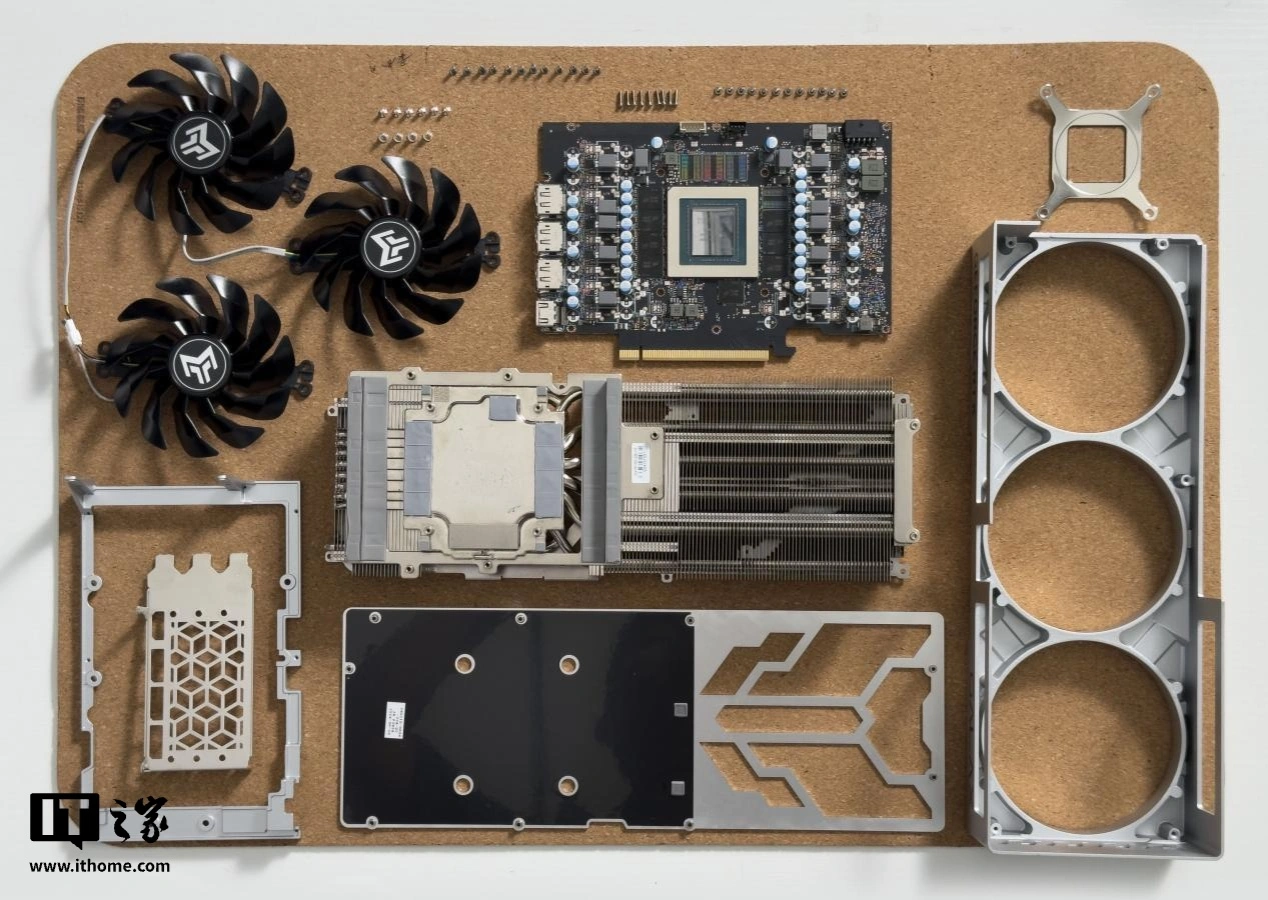

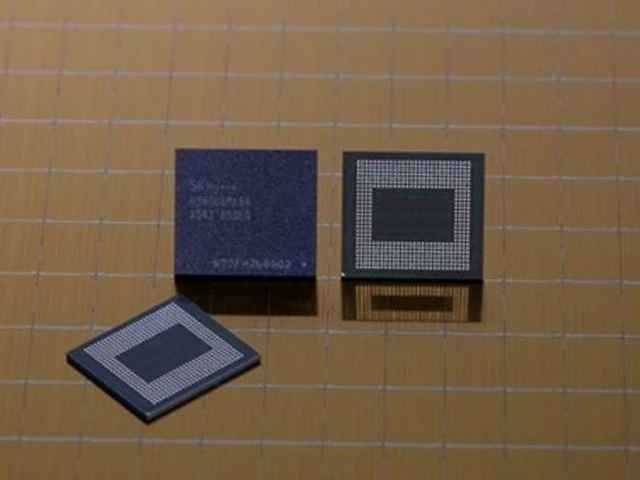

实践运用中,降低工作电压,优化时钟速率以及采用节能模式,能显著控DDR3内存模组之能源消耗;同时,高级制程技术亦可在芯片级别上贡献降低能耗,提升系统综合性能表现。

此外,DDR3电路设计需兼顾动态功耗管理技术的运用。该技术能依据系统负荷灵活调整能耗水平,实现节能环保的同时,提升设备耐用性。

仿真与验证在DDR3电路设计中的作用

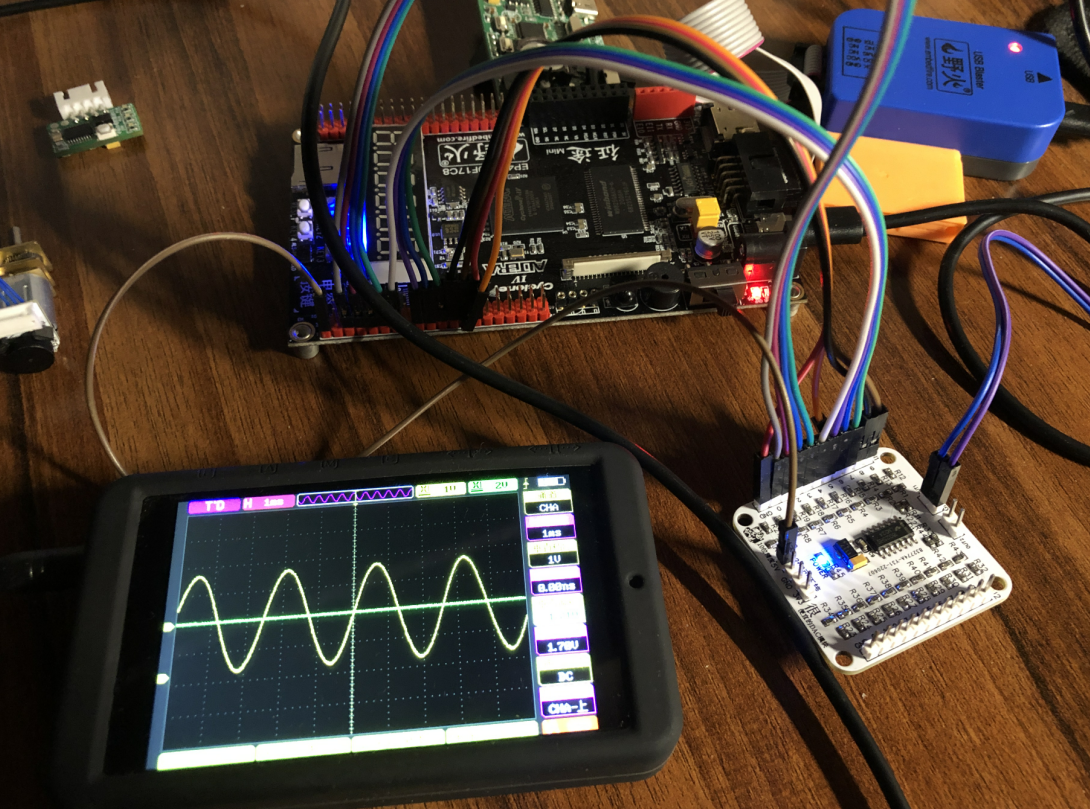

在高端系统设计领域,仿真与验证起着关键作用。基于此,DDR3电路设计亦然。事前模拟验证能为工程师抢先识别潜在缺陷并顺利修复。

借助仿真实验,内存模块可精准呈现众多工况下的运作状况,进一步评估其稳定性能及可靠性。进而,此种设计方法有助于优化布局布线策略,调整关键参数以符合产品特性,且极力降低后期修正措施所产生的额外经济负担。

在此过程中,需严格进行验证环节的验证测试,包括时序分析、眼图测试及噪声容限分析等多个方面。唯有全方面精确检验后,方能确保DDR3内存模块在多元化工作环境中的稳定性和可靠性得到充分保障。

未来发展趋势与展望

面对科技日新月异与市场需求持续高涨的双重挑战,DDR3内存这一古老而又强大的存储器依然焕发勃勃生机。展望未来,DDR3电路设计领域将涌现出更为创新的技术手段与解决策略。

在未来,DDR3内存模块将更趋智能化和自适应化;其数据传输速度将会更快,功耗将得以降低;并且,安全性也会得到极大提高,通过强化数据加密来应对日益严重的网络安全威胁。

在科技进步和创新驱动的双重影响下,DDR3内存模块将面临更多机遇与挑战。唯有持续学习知识和跟踪行业动态,方能更好应对未来变革、立足市场前列。