1. DDR2 PCB布线规则概述

DDR2作为常见内存之一,其PCB设计中的布线原则对提升设备性能及稳定度具有关键影响。在执行该布线设计过程中,信号完整性、电磁兼容性以及能耗等均须得到充分考量。首要策略在于,合理的布局及连线能缩减信号传播路径,降低交互干扰与延迟,从而提升数据传送速率;其次,理想的布线规划有助于减少串扰及反射现象,增强抗干扰能力。

DDR2 PCB布线下需关注差分对长度匹配、走线宽窄、阻抗调控及地孔设计等要点。长度匹配可降低时延不均与串音及时序故障发生率;选择适当走线宽度有助于提升信号传输品质与节能效果;进行阻抗管控能确保信号健全且避免反射增加;设定恰当地孔目的在于实现优良的接地联接并减少地回路阻抗的产生。

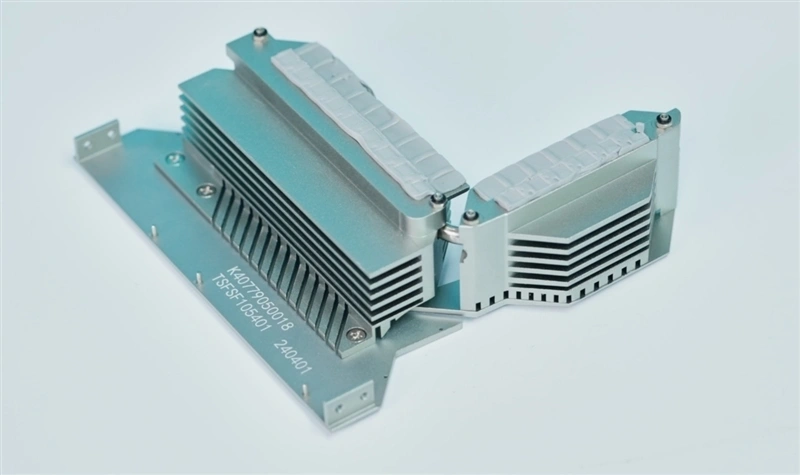

2. DDR2布线层次结构

在DDR2印刷电路板(PCB)布线设计过程中,为了满足信号传输需求,常采用多层板结构。常见的DDR2布线分层结构包括信号层、电源层及地层三大部分。信号层主要负责线路走向以及内存芯片与控制器等元器件间的连结;电源层为系统供以稳定的电力支持;地层则构建了完整的接地网络体系。

在DDR2 PCB布线设计过程中,应明智地安排各层之间的堆积次序,控制间距及引脚联结机制。妥善堆积可减轻串扰与电波干扰,恰当的间距有助于减小板内串扰,准确的引脚衔接能够提升信号完整性同时减少反射现象。

3. DDR2时序约束与布线

DDR2内存对时序要求严格,PCB布线需重视。设计包含时钟分配及数据/地址/控制信号传输路径长短相同等规定。合理的时序能保障数据传输稳定可靠。

在DDR2印刷电路板(PCB)布线环节,必须依据内存芯片制造商所规定的时序参数来确定走线方案,并借助仿真软件测试以确保设计达到标准。此外,在满足时序要求的基础上,还需兼顾阻抗管理、差分对匹配等多元要素,以便取得最佳效果。

4. DDR2 PCB布局技巧

除布线规则外在设计DDR2 PCBA时,优良的布局乃是保证系统性能及稳定性的重要因素。需关注以下几个要点:1.内存芯片和控制器应尽量贴近以便减少信号传输路径;2.用心排布电源与地连线以保障供电稳定性;3.减少交叉信号和锐角折弯以降低干扰可能性;4.余出足够空闲区域安置所需滤波器或终端电阻。

运用上述策略,我们能够在DDR2电路板设计中显著降低系统噪音,增强其抗干扰性,从而确保数据传输的稳定性和可靠性。

5. DDR2 PCB仿真与调试

完成DDR2印刷电路板设计之后,需进行仿真核实及调整以保证其满足预期性能标准。利用模拟技术检验信号完整性、时序要求以及阻抗配置的核心要素,并据此进行合理调整与优化。

实际调试过程中需借助示波器、逻辑分析仪等设备,对数据传输质量进行严密监控与分析,并不断优化设计参数以达成最优效果。经严谨的仿真验证及实测调整,方能使DDR2 PCB设计取得理想效果。

6. DDR2 PCB布线常见问题与解决方法

DDR2 PCB设计的过程中,可能遭遇诸如串扰、反射及阻抗失配等难题。为迎刃而解,需针对性地实施相应对策,如加大差分对间距离以缓解串扰影响,或是运用屏蔽罩对抗干扰;对于反射现象,可通过增设终端电阻或者优化走线路径予以消除;至于阻抗失配的问题,则可以利用调整走线宽度或修改堆叠方式进行优化。

妥善处理上述常见问题,可提升DDR2系统功能及护航数据传输品质。

7. DDR2未来发展趋势

随着科技飞速进步,DDR2 内存技术的持续优化和发展成为必然。预见之下,高速度、低能耗、紧凑型的 DDR2新特性产品将逐渐面世。此外,PCB 设计的需求亦将面临更为苛刻及复杂的挑战。

未来趋势要求我们持续补充行业新知及技能,将其适时应用于实际项目。紧随市场动态脚步,以求创新和发展,方能在激烈竞争格局中保持优势地位。