1. DDR3内存概述

DD3内存作为常见的计算机存储设备之一,具备高带宽与优良性能特性。该类内存采用双倍数据速率技术,在每个时钟周期内能传输两组数据,不仅拥有更高速率,且功耗更低。如今,尽管有新型内存技术涌现,但DD3仍在众多计算环境下发挥着重要作用,尤以需要高效性能支持的领域为例。

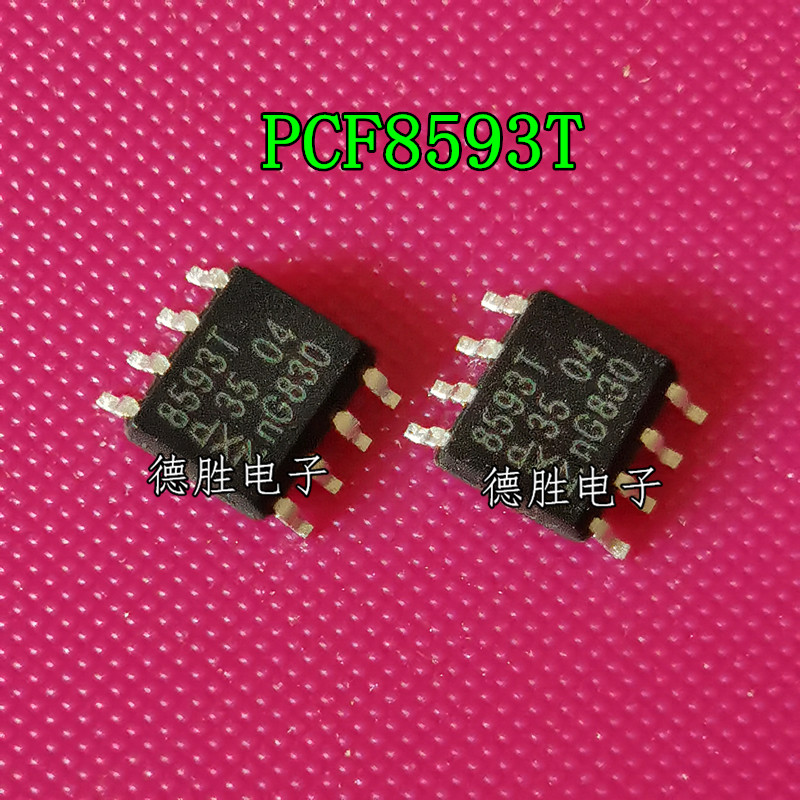

DDR3内存模组主要由多颗DRAM芯片构成,每一枚芯片内部亦含有无数个存储单元,它们即可存放一个个的数据位。通过严格遵循时钟周期的读写,便可完成对内存内容的操作。此款模组内部配置有对应的地址线与控制线,使得地址信息和控制信号得以精确传递。

DDR3内存需兼顾信号完整性、功耗与时序等层面,其精心设计有助于提升系统性能及稳定性。

2. DDR3设计流程

DDR3设计流程主要涵盖需求分析、架构规划、电路创制、物理设置、以及验证审核等环节。为保证设计高效实施,需首先明确系统对于内存的多元需求,特别是对带宽、存储空间及延迟等核心参数的严格把控。架构设计则依赖于清晰了解内存模块的总体构造与部件接驳方案。

在DDR3系统设计中,电路布局尤为重要,需依据相关标准设置数据线路、时钟线以及控制线等环节。在此过程中,必须注意信号完整性、能耗及抵抗外来干扰的能力。而实体布线阶段便是将电路设计解析成为现实中的印刷电路板(PCB)布局。在此阶段,应对信号传递路径长度匹配、接地线与电源线规划予以充分考量。

验证环节乃是DDR3晶元设计中的关键步骤,借助于仿真及实践测试,对设计的适宜性进行确认与核实。唯有经过充分验证后,方能保障DDR3内存模组在实际场景中保持良好的运作效能。

3.信号完整性分析

DDR3内存因其高工作频率引发复杂的信号完整性问题,这给信号传输带来严重挑战,诸如反射、串扰及时序偏移等不良因素均有可能影响信号质量。因此,对信号完整性的深入研究与分析尤为关键,力求保障信号质量符合预期标准。

信号完整性分析涵盖了传输线特性阻抗匹配、终端匹配及走线长度匹配等关键环节。借助仿真软件的强大功能,我们得以对信号传输路径进行精细建模,从而挖掘并排除潜在问题。同时在实际PCB布局设计过程中,应重视走线规划策略以及层间堆叠方式,尽量缩小信号传输路径长短差异。

同时,信号完整性评估需关注时钟和数据同步、时序偏移等因素。精心设计并确保时钟树的有效性及各时序参数符合规定标准,力图提高系统稳健性。

4.功耗优化策略

在现代计算机体系结构设计中,功耗问题不容小视,尤其是对于DDR3控制器设计来讲,实现高效节电的节能机制刻不容缓。

DDR3设计中的功耗包括静态功耗与动态功耗两部分。其中,静态功耗源自芯片静态运行时能量的损耗;而动态功耗,实质上是由工作过程中因充放电产生的能源消耗所决定的。

为降彽静默状态的电量消耗,可在芯片制作过程中选用低功耗技术,同时优化电源管控模块;动态功耗部分,则需探索减小负载、完善时序参数等措施以降低充放电能耗。

在实际布局中,科学合理地构建电源与地面网络架构可显著减少能耗的流失,且运用前沿的散热科技能进一步降低功耗损耗。

5.时序约束设置

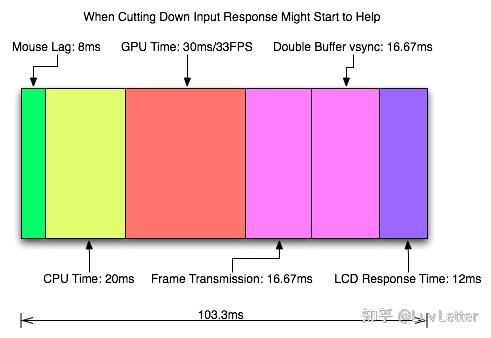

时序约束在DDR3设计中的重要性不容忽视,其设定的质量直接影响着数据写入以及读取的可靠性,同时也关乎各操作能否如期顺利执行。

时序约束的设定与读写操作间多个参数有关,如CAS延迟时间和预充电时间等调节。此外,还要调整时钟树结构,运用各种校正技术,惟有如此,方可保证系统的正常运转。经由仿真验证这些约定义务的正确实行才是关键。

在实际运用环境里,我们不能忽视温度波动和负载变动对时序的影响与时序稳定的潜在问题,因而在设定时序约束条件时必须综合考虑并妥善处理。

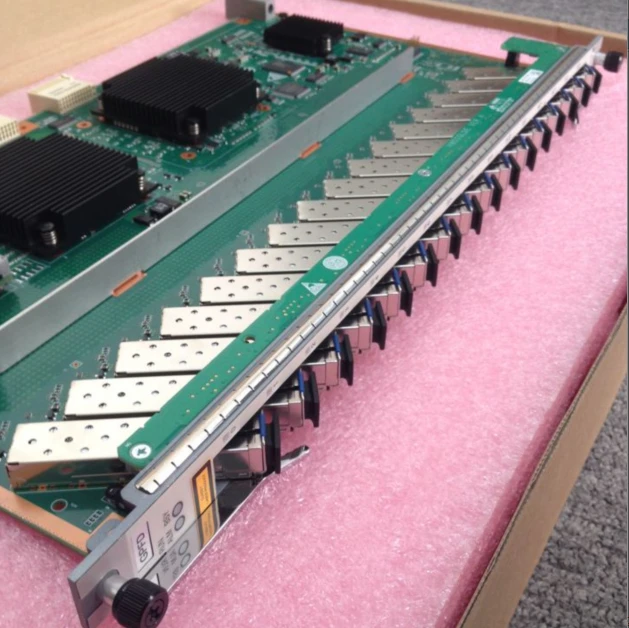

6. PCB布局技巧

PCB布局,作为DDR3设计中的关键环节,具有显著提高系统稳定性与抗干扰能力的重要作用。在实施 PCB布局过程中需重视以下几点:

首要条件乃电缆长度匹配,确保各条数据线上的距离相等以降低信号传递的时间差。第二点在于接地网络设计,在印制电路板(PCB)上巧妙布置地网结构能显著降低地电位回馈路径的阻抗并提高系统稳定性。此外,还需关注如何进行供电网络布置以及如何选配差分对布线方法等细节问题。

除了上述要点之外,PCB布局时亦须关注串扰问题,尽可隔离数模转换器和数字区域实施妥善的屏蔽措施;务须谨慎考虑边缘走线及层间跃迁形式,以降低串扰影响。

7. DDR3测试与调试

DDR3设计成功之后,必须执行全面的测试及调式流程,以保证其高质量运作。这些过程涵盖了必备的功能性评估、性能测定以及稳定测试等关键环节。

功能测试旨在验证DDR3内存模块的所有功能是否符合标准,探寻硬件中可能存在的问题;性能测试旨在检验其读写速度是否满足公开指标,并精准评估出实际性能水平;至于稳定性测试,它通过长时间的连续运作来测试模块在各种复杂环境中的稳固可靠性。

调试工作聚焦于诊断及解决问题,涵盖硬件与软件两大部分。唯有严格执行相关测试和调试步骤,并妥善处理潜在问题之后,方能交付产品或投放市场。