DDR(双倍数据传输率)作为一种高效的内存技术,其电子特性对其性能及稳定起到了关键作用。本篇文章将详细剖析DDR电子特性的各个层面,如信号完整性、时序分析以及能耗等,旨在揭示DDR内存的深层原理。

信号完整性与噪声

DDR内存的信号完整性,主要涉及数据传输阶段内信号质量及稳定性。鉴于其工作频率极高且易受各类噪声干扰(如串扰、反射),故确保信号完整性对DDR内存正常运行至关重要。

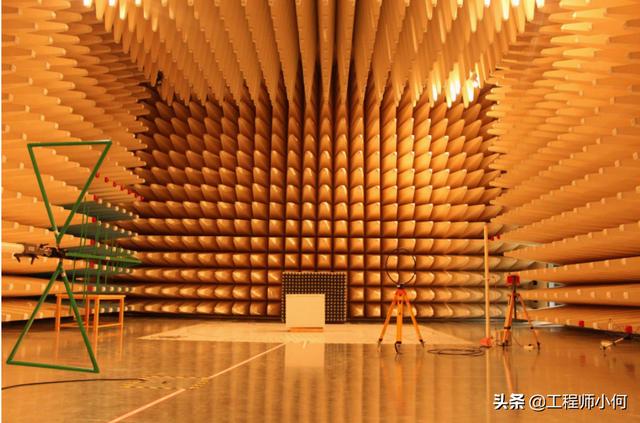

为降噪,DDR内存设计普遍采用布局规划、信号层拆分与终端阻抗调整技术。此外,借助设计阶段的电磁兼容性仿真及分析,可有效预见并解决潜在的信号完整性问题,从而保障DDR内存系统在高频环境中的稳定运行。

此外,DDR内存控制器中所采纳的信号预留时间(SetpupTime)及保持时间(HoldTime)等严格的时序规定,同样是保障信号稳定性的关键要素。恰当设定这两类时序规则,可有效规避数据传输期间的时序矛盾,提升DDR内存体系的运行稳定性与性能表现。

时序分析与时钟树设计

时序分析在DDR内存设计中扮演关键角色,主要用于优化时序路径,保证数据能在预定的时间窗口内准确传输到指定位置。此过程涵盖了数据传输路径、时钟路径以及控制路径等多个方面。

为确保DDR内存时序需求得到满足,需进行有效的时钟树设计与优化。这其中包括时钟源的筛选、时钟资源的合理分配以及时钟缓冲器的配备等环节,以期降低时钟信号的时钟偏移及抖动,从而提升时钟的稳定性与可靠性。

时序分析进程需考量时钟周期、时钟延迟与时钟抖动等要素,为确保DDR内存系统在各类工况皆符合时序需求,应有针对性地进行严格仿真验证。进一步,可借助时序补偿及优化等技术措施,以提升DDR内存系统的性能与稳定性。

功耗分析与热管理

DDR内存功耗,作为其性能及稳定性能的关键指标之一,主要由静态及动态两个方面组成。静态功耗主要源自存储芯片的静电流及其内部电路消耗;动态功耗则主要源于数据传输过程中的电荷翻转与信号驱动等环节。

为科学管控DDR内存能耗,需从设计与布局两层面着手。在设计阶段,可通过改善电路架构、降阶电压等途径达到节能效果。接着,在布局环节,可以运用高效的布线布局、完善的供电网络等策略,有效应对功耗分配不均引发的过热问题,从而提升DDR内存系统的稳定度与可靠性。

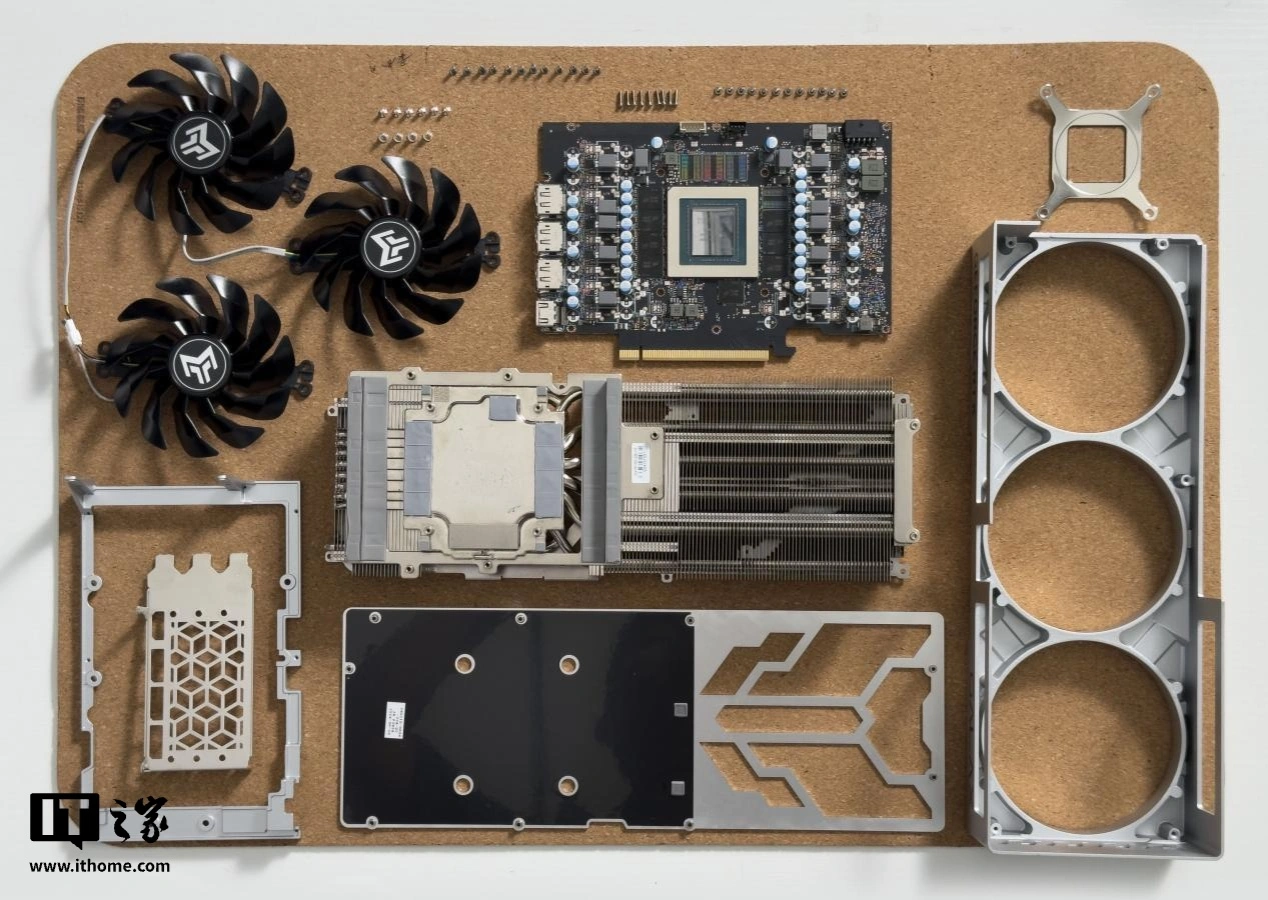

在应对DDR内存热管理问题上,采取散热片与风扇等主动散热措施,或者借助科学的布局与供电网络规划,降低功耗集中区的温度梯度,从而有效控制DDR内存系统温度,提升其性能及稳定性。

DDR与系统集成

DDR内存作为计算机系统内核的关键组成元素,其电气属性直接影响整体系统的性能和稳定表现。故而,在DDR内存系统的设计过程中,必须全面考量其与其他硬件设备的协调配合。

在系统整合进程中必须着重关注DDR内存与处理器、主板及外设等硬件间的连接界面及其通信协定,这有助于系统总体性能以及稳定性的提升,并能够实现对DDR内存的出色包容性。

在此基础上,我们必须深入研究DDR内存在整个系统运行过程中对功耗的分类和热能管理的影响。通过精心设计供电网络并优化功耗分布,我们有可能显著降低系统能耗及温度,从而提升系统稳定性和可靠性,最终达到DDR内存与系统的完美融合。

DDR未来发展趋势

在计算机科技的持续进步下,DDR内存正经历着深刻的演变与升华。其发展方向可预见的有以下几点:

加速前进:伴随着数据传输速度的提升,DDR内存的运转频率亦不断提高,以满足日新月异的计算需求。

低耗节能:面向未来的DDR内存将致力于降低功耗与能耗,通过创新的制造技术及电路设计,以实现更低的能耗以及更高的能效比。

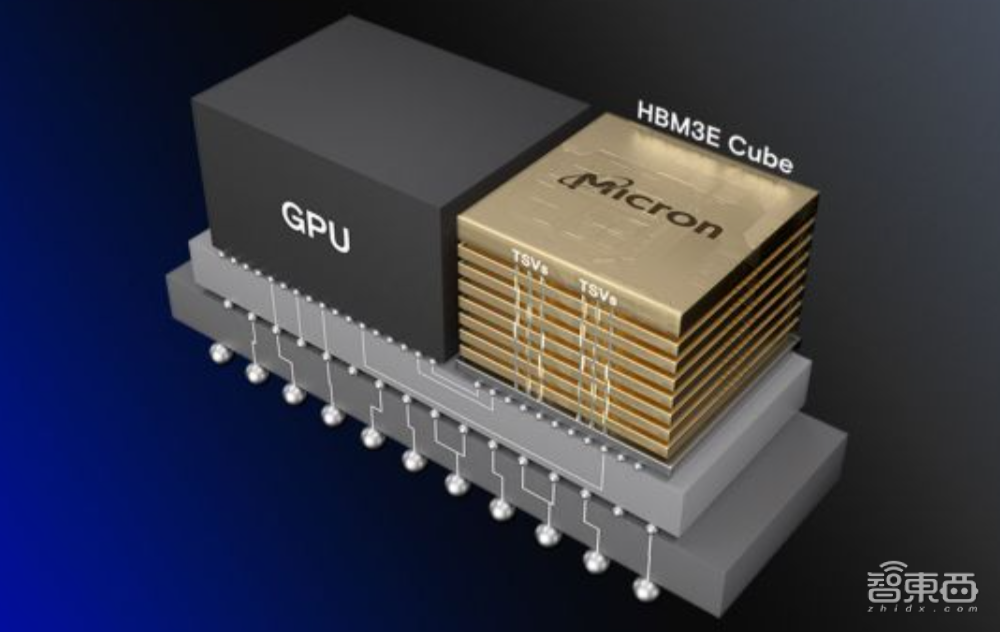

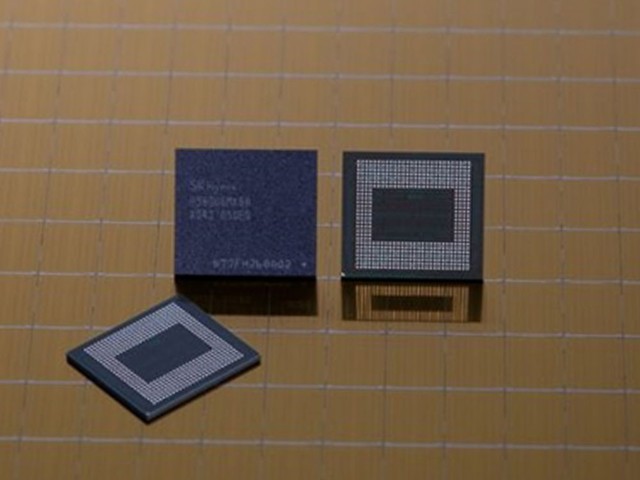

扩大容量:受数据量持续增长驱动,DDR内存将逐步实现更大的储存空间,以满足大型数据处理及储存需求。

卓越可靠度:面向未来的DDR内存将专注于提升系统的可靠性与稳定性,运用更为坚固的设计及制造技术,增强内存系统的抗干扰性以及容错性能。

借助持续创新与技术升级,DDR内存在计算机体系中,始终占据核心地位,为数字时代的繁荣发展提供坚实后盾。