身为热衷于技术研究的工程师,我对DDR3与FPGA的集成颇感兴趣,DDR3作为目前主流的内存类型,其与FPGA的融合会引发哪些创新及挑战?我们一同深入探讨DDR3在FPGA中的应用,揭示这项技术的奥秘。

1.DDR3与FPGA的基本概念

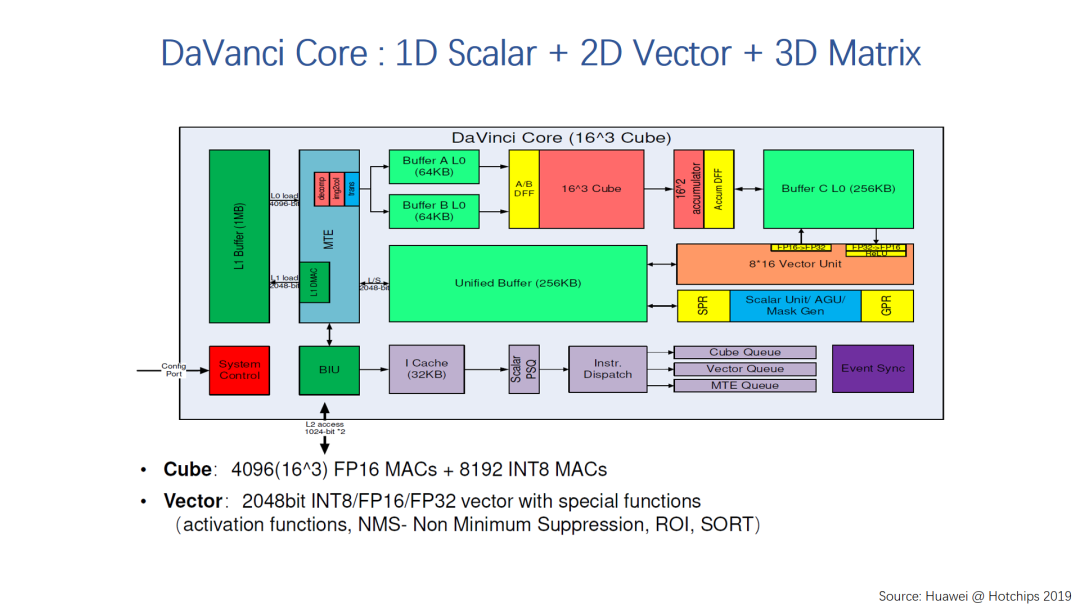

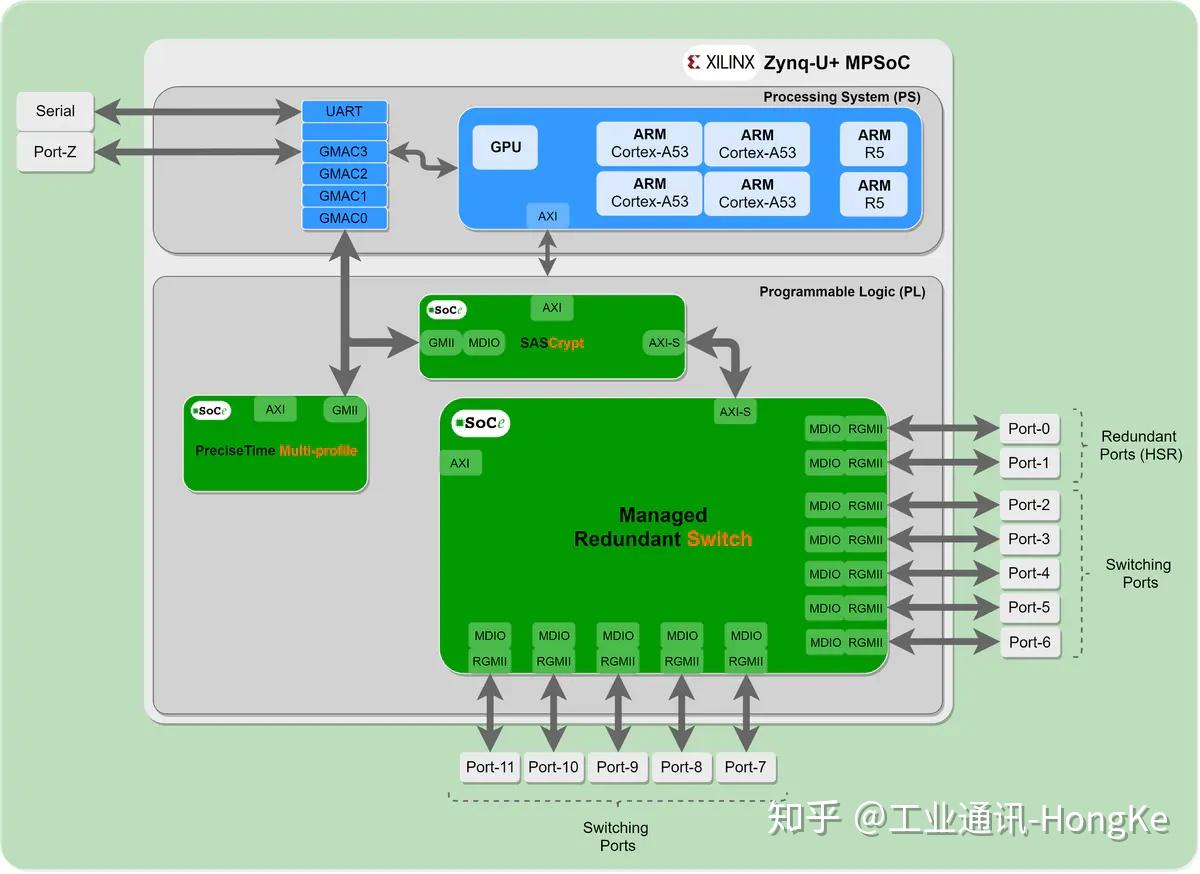

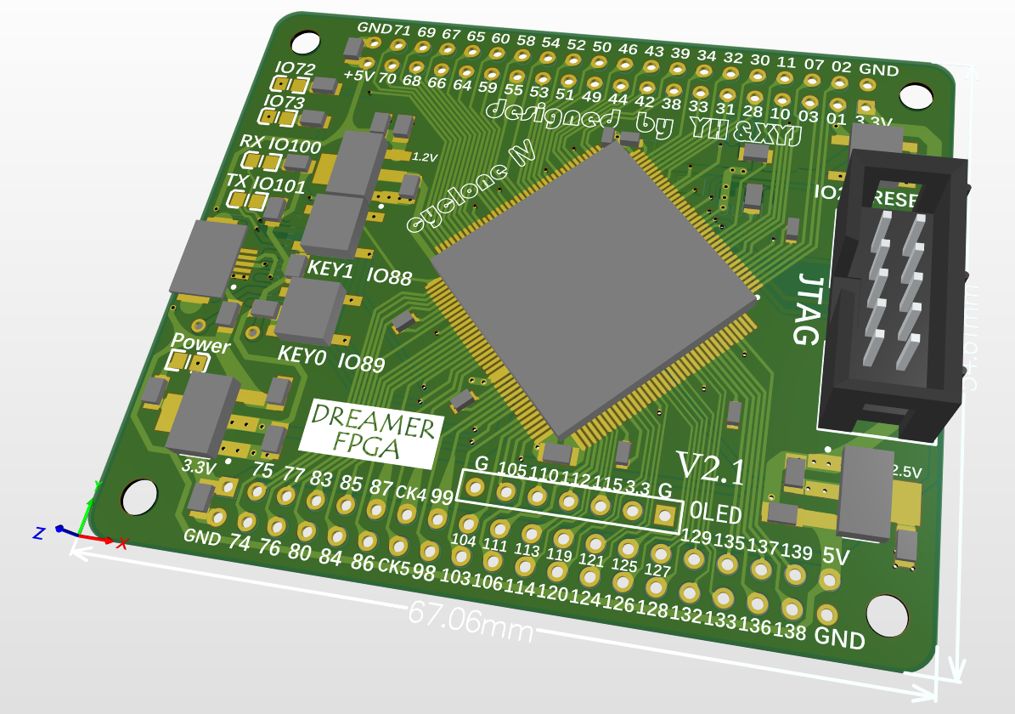

首先,让我们详细了解DDR3与FPGA的基础知识。DDR3为双数据速率同步动态随机存取存储器,具备高速传输及低能耗特性,广泛运用于计算机与通讯等领域。FPGA(FieldProgrammableGateArray)则为可编程逻辑器件,其灵活性与适应性极佳,可依据用户需求进行现场编程。

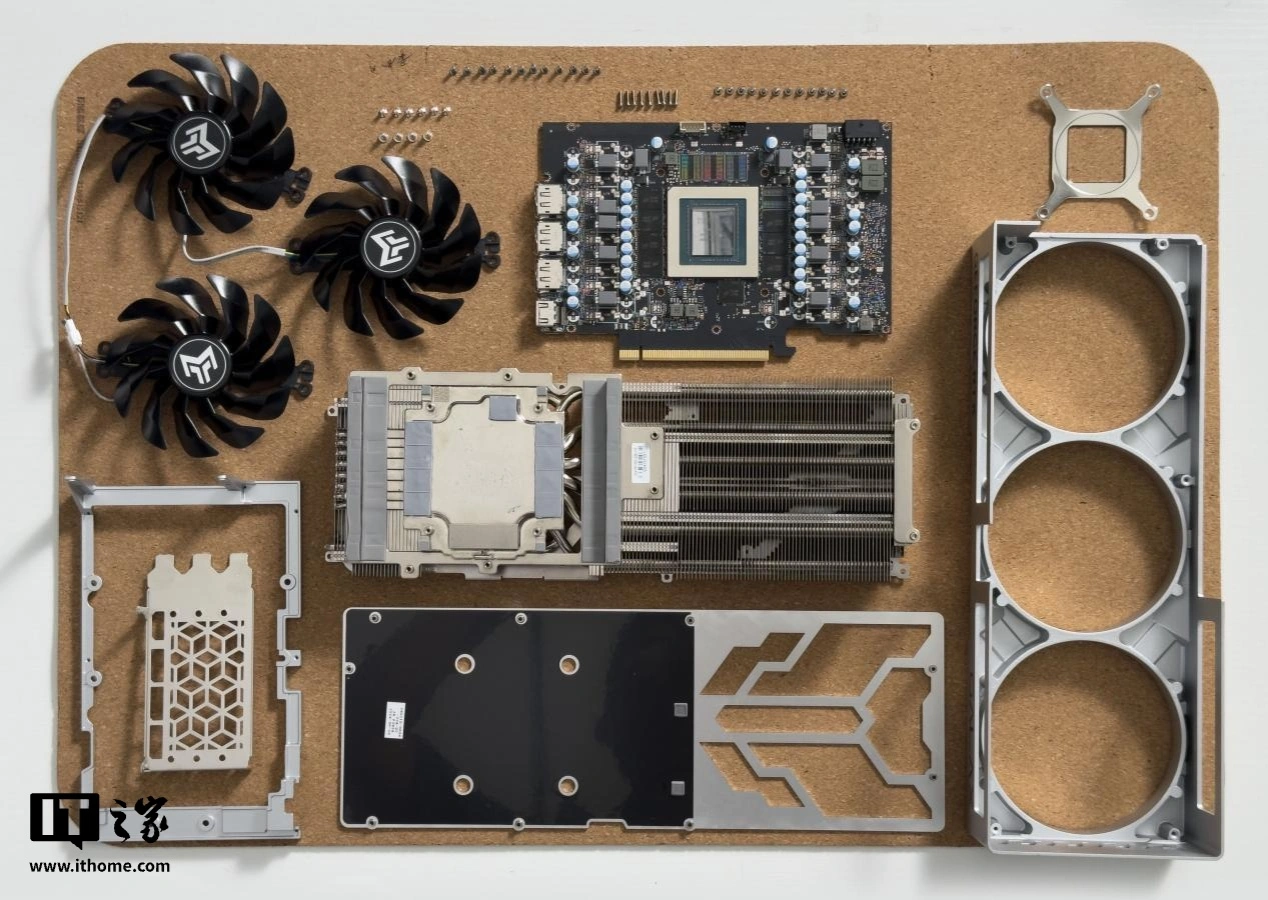

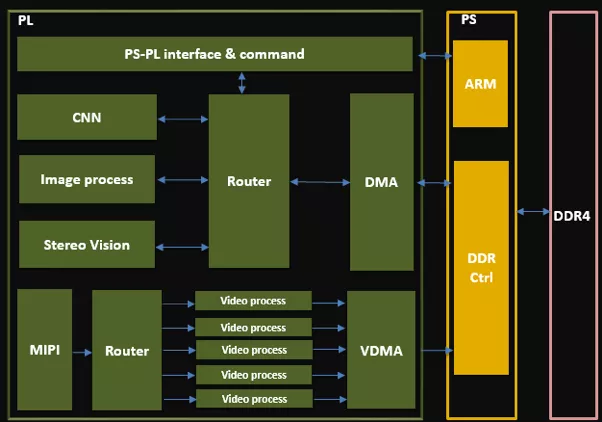

DDR3模式的FPGA外部存储与FPGA相连,以高速接口保证数据迅速传递和高效处理。FPGA作为核心处理器,可调控DDR3的读写行为,确保整个系统稳定并提升其性能表现。此整合方式将记忆体与执行逻辑处理的功能单元紧密结合,为系统设计提供了更广阔的发展空间。

2.DDR3的FPGA应用领域

DDR3FPGA技术被广泛运用于多领域,如通信设备、图像处理器以及人工智能领域。其中,在通信系统中,FPGA可提高数据处理及传输速率;在图像处理部分,DDR3FPGA能够实现高分辨率与高速率的图像处理;而在人工智能方面,FPGA则能助力神经网络的训练与推理,从而加快AI算法的执行速度。

曾主导DDR3FPGA项目,旨在构建高效能数据采集与处理系统。此项目中,我们善用DDR3的高速传输优势,结合FPGA的灵活性及可编程性,成功实现数据的迅速采集与实时处理,有效解决客户实际问题,同时加深了本人对DDR3FPGA的理解与认知。

3.DDR3的FPGA设计考虑

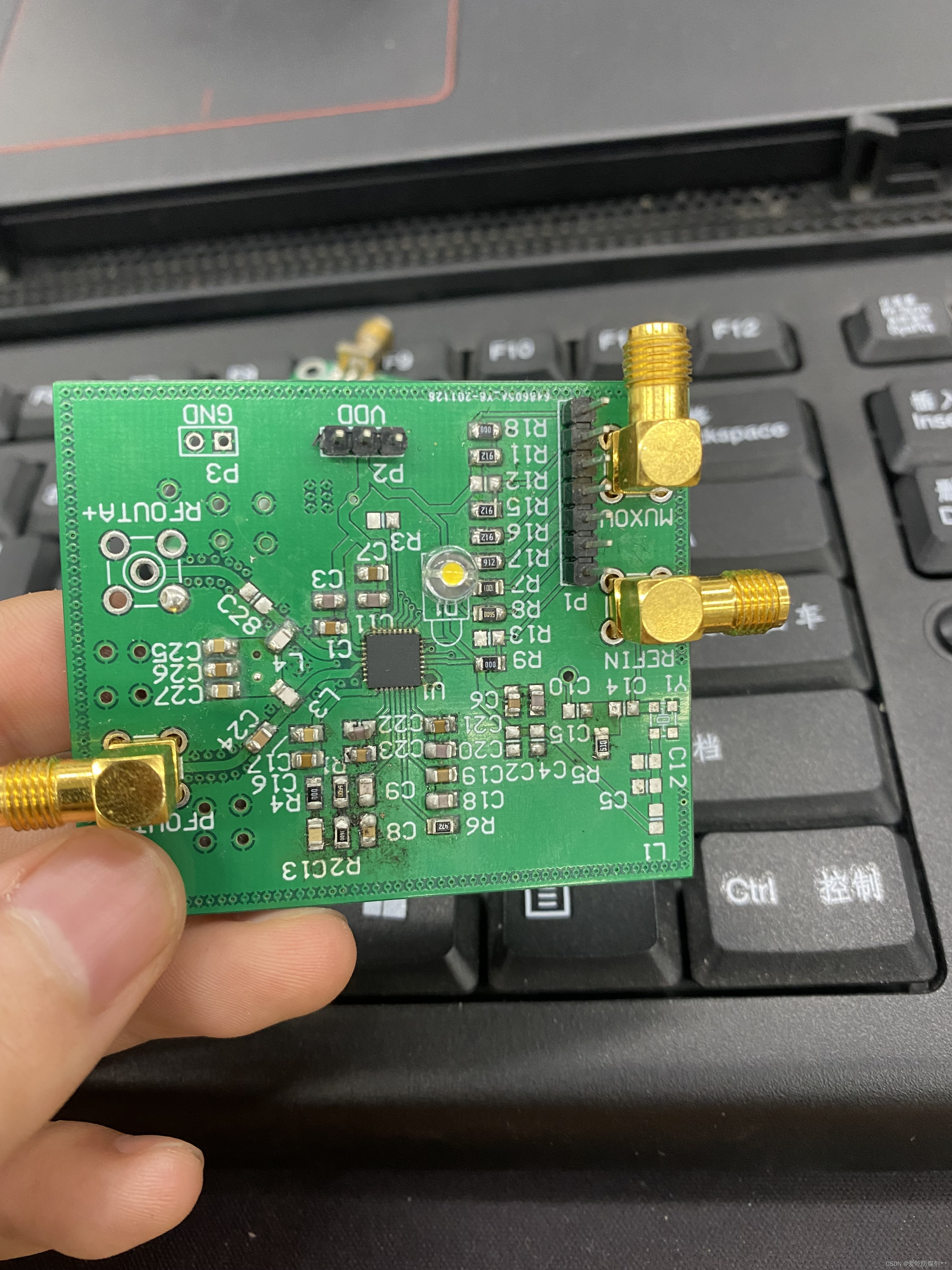

在进行DDR3FPGA设计之际,需关注诸多要素,如时序约束、布局布线及功耗优化等。时序约束即确保设计符合DDR3时序规范,以保障数据稳定传输与准确接收;布局布线则涉及在PCB设计中,对DDR3与FPGA引脚及信号线进行科学安排,降低信号传输延迟与损耗;而功耗优化则强调在设计过程中,充分考虑系统能耗问题,力求降低功耗,从而延长设备使用寿命。

在以往项目中,由于时序限制未得到遵守,导致DDR3与FPGA间的通信不畅,数据传送不稳。经过团队不懈努力及紧密协作,我们成功找到并实施了解决方案,即调整时序限制,确保数据准确无误地传输。此次经验使我对时序限制设定有了更深认识,同时也深化了对DDR3FPGA设计的理解。

4.DDR3的FPGA性能优化

为充分提升DDR3配合的FPGA性能水平,需进行深度的性能优化工作,主要包含以下三个层次:时序优化,资源运用优化以及功耗优化。时序优化旨在通过科学的时序设定与限制,以增强系统的时序稳定性及可靠性;资源运用优化则是通过对FPGA资源的高效利用,减少资源占用,从而提升系统性能并提高运行效率;而功耗优化的核心在于降低系统能耗,从而延长设备使用寿命。

在高性能需求项目的研究中,我们开展了DDR3的FPGA性能优化实践。经过细致的时序调控,优化资源配置,降低能耗,成功提升了整体系统性能并降低了能量损耗。此次经历使我深刻认识到,性能优化对于DDR3FPGA设计具有举足轻重的地位,同时也深化了我对性能优化策略与技术的理解。

5.DDR3的FPGA未来发展

伴随着科技持续地创新与深化,未来的DDR3FPGA将拥有更广泛且具潜力的发展领域。然而,面对如DDR4、DDR5等新世代存储器的崛起,DDR3FPGA将迎来诸多挑战及机遇并存的局面。展望未来,DDR3FPGA或将更加重视性能、能耗以及安全三者之间的均衡,同时也可能加强与人工智能、物联网等新兴技术的融合。

本人怀揣对DDR3FPGA未来的热切期盼与向往,誓要在新项目里深掘并运用此技术,以此推动技术革新,尽献绵薄之力。