自进入计算机硬件行业以来,DDR5内存的最低时序便成为了我的关注焦点。夜间独处之时,我常投入于研究复杂的时序并解读闪烁的数字,以期揭示DDR5内存的极致性能。今日,在此与诸位共享我的探索心得,期待激发您们对硬件科技的热爱。

初识DDR5:内存的新篇章

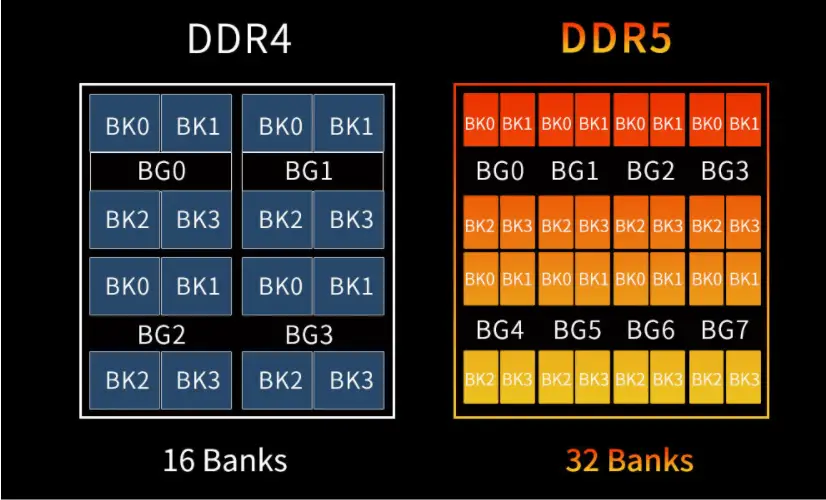

初次了解DDR5内存,其卓越性能指标令我震撼。对比DDR4,DDR5实现了速度与能耗时序的重大突破。我对此产生了浓厚兴趣,深入研究每一环节,涵盖芯片设计、封装工艺乃至性能测试等领域。在此过程中,深刻认识到最低时序并非单纯技术参数,而是内存性能的核心要素。

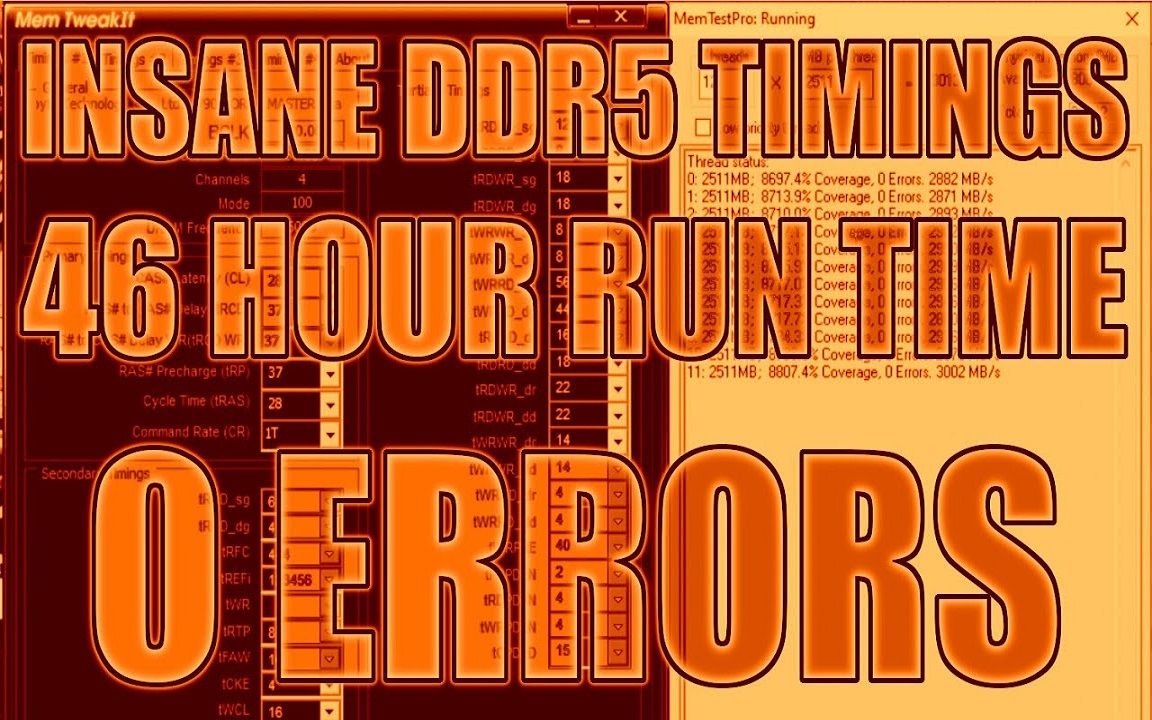

深度剖析DDR5的时序设定后可见其远超越DDR4之繁琐。各项微小调整均能对性能产生重大影响。此非纯学术问题,更接近于精细艺术的实践。抛开物理层面,进阶至BIOS或软件端进行時序调节及动态内存监测。每次调试过程犹如与内存共舞,精心策划,精益求精。

探秘最低时序:技术的边界

追求DDR5最低时序的道路上,面临诸多挑战。硬件制约首当其冲,各异的板卡及处理器对于内存的支持程度各有差异,导致可进行时序调整的余地受限。为此,必须深谙各类硬件的兼容特性,方能寻得最佳设定方案。此过程既具挑战性又颇具成就感。

同时,控制温度与电压同样至关重要。相较于DDR4,DDR5对于工作环境更为敏感,细微的温度或电压变动均可能引发时序不稳定现象。因此,精确掌控此类外在条件变得尤为关键,以便保证内存能够保持良好运转状态。

实战演练:从理论到实践

实践为理论提供了真理的标准。我在各类实战环境下对内存设定进行严格评估,无论面对繁重的数据处理挑战,或是尝试最新款的3D游戏,始终竭力实现DDR5内存的最高性能表现。每次实验的成功,都加深我对最低时序重要性的理解和相信。

在此过程中,本人掌握诸多优化内存性能的妙法,如通过调节指令速度与数据传输率以保证稳定运行之余实现性能提升。凭借这些实践心得,使本人对DDR5内存有了更为深入的认识。

挑战与未来:DDR5的潜力

虽已有所成,但仍深知DDR5内存之潜能尚未尽数释放。随着科技推进,低功耗、高速的工作时序将有望成为现实,内存性能亦将进一步提升。我对此领域的发展前景和自身的努力充满期待,誓言继续在此领域矢志不渝地投入研究与实践。

在追求DDR5内存最低时序的过程中,我深入学习相关技术,深刻理解了坚持与挑战自我的必要性。无论是挫折还是收获,都使得我对这个充满斗争和机遇的行业产生更深的热爱。

文章结尾:

通过此文,期待您能深入了解DDR5内存及其最小时序标准。此领域发展日新月异,每次探索皆孕育无尽惊喜。现提出一问:在您的个人电脑运用体验中,是否曾涉及独特时序调整或性能优化操作?诚挚邀请您在评论区分享宝贵经验,共同探讨未知领域!请不要忽视点赞与分享,吸引更多同好参与讨论!