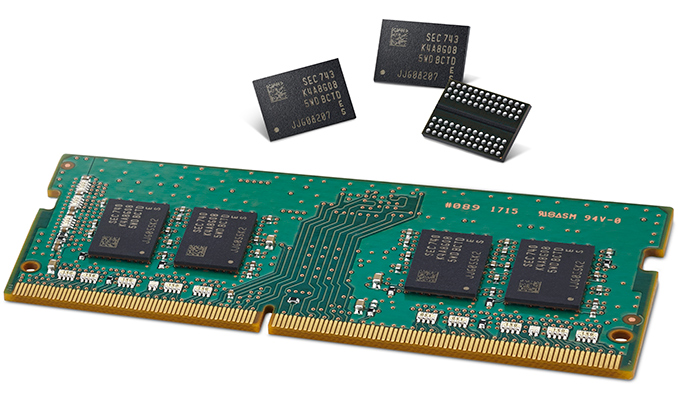

DDR2与DDR3为现代电脑内存的核心标准,其布局设计对系统性能与可靠性起到决定性作用。本文将全面解析DDR2与DDR3布局的关键技术,以助读者深刻洞察这两种内存布局的需求与设计理念。

1.DDR2与DDR3的基本概念

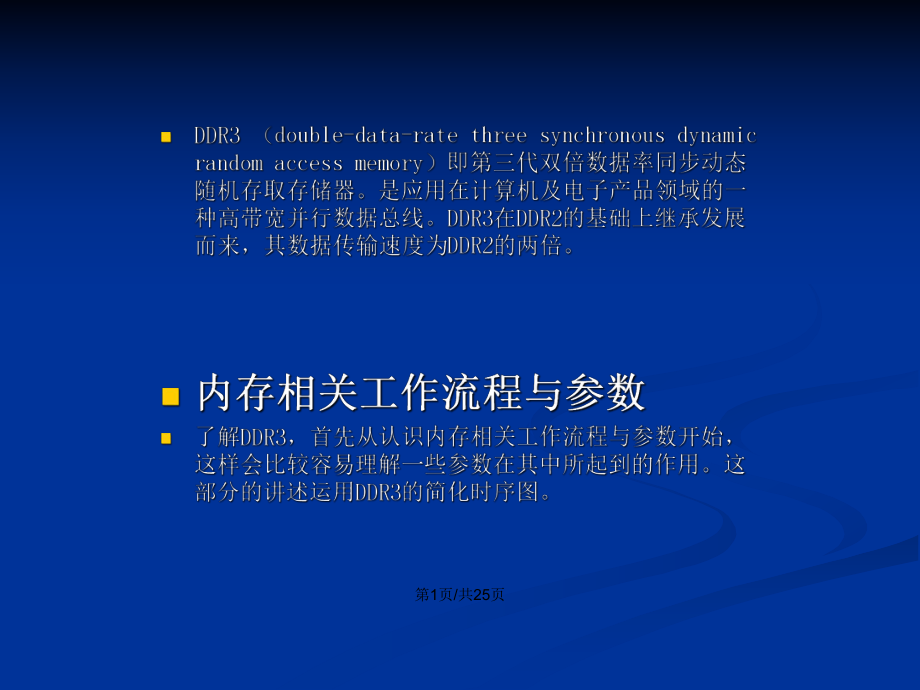

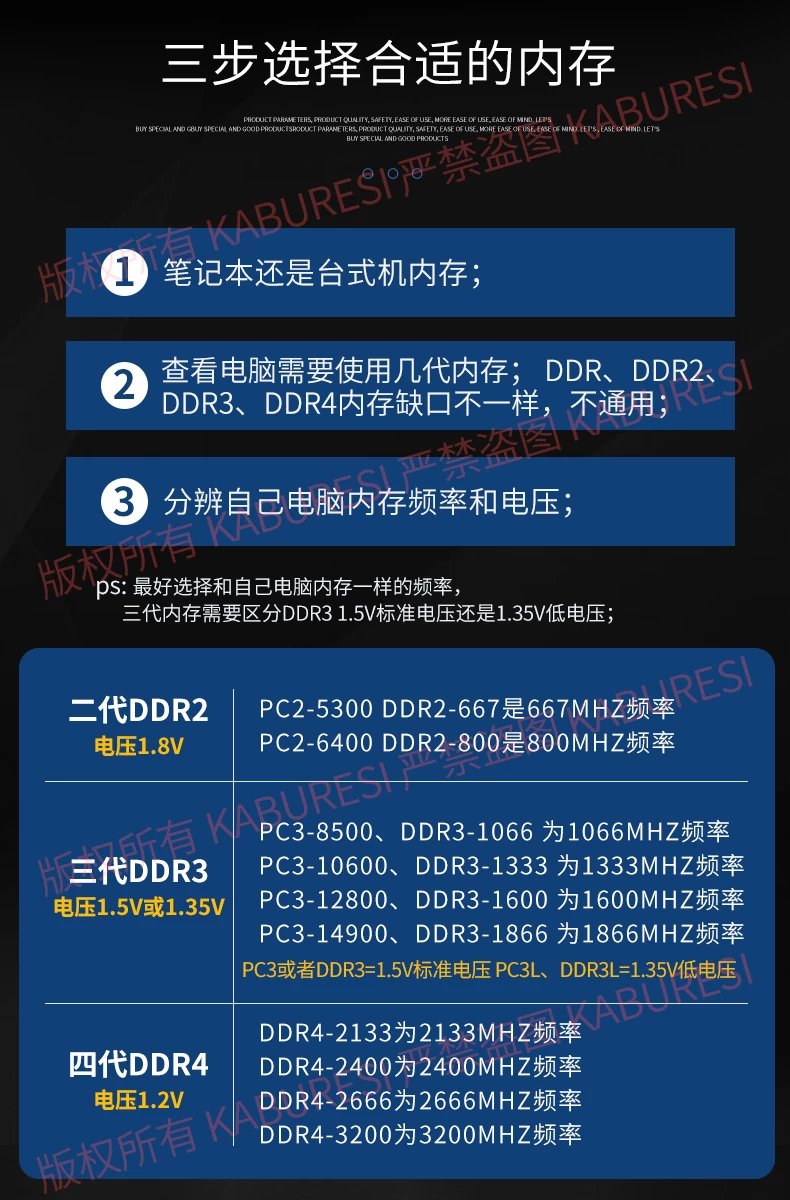

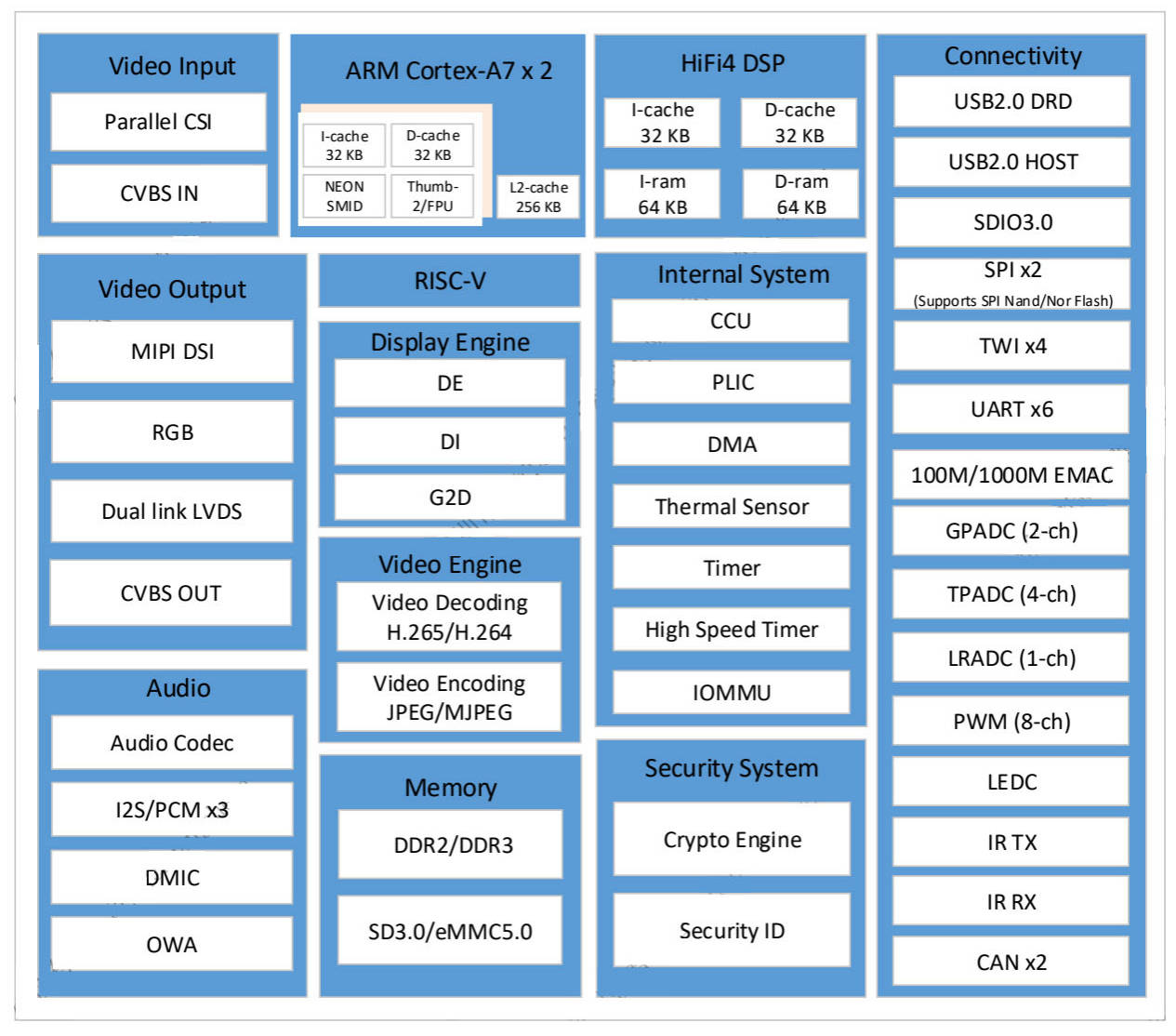

DDR2及DDR3为双倍数据速率内存的第二代和第三代规格。DDR2的工作频率通常介于400MHz至800MHz,而DDR3的工作频率范围为800MHz至1600MHz。这两种内存技术的关键差异体现在数据传输效率、电压及功耗上。DDR3在数据传输速度及电压需求方面优于DDR2,从而在功耗及性能方面实现显著提升。

在布线设计中,掌握DDR2与DDR3内存的基本运作机制及其特性极为关键。这两类内存的布线需求存在差异,尤以信号完整性、时序处理及电源操控为要。设计者须依据内存的具体规范来优化布线策略,以实现系统稳定运行和性能提升。

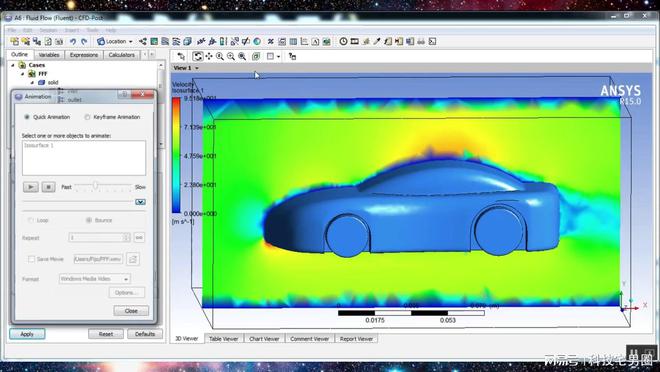

2.信号完整性要求

DDR2及DDR3布局中,信号完整性至关重要。鉴于DDR3运行频率更高,传输速率加快,其信号完整性要求愈加严格。信号完整性相关问题主要涵盖反射、干扰及计时误差等。

DDR2布线普遍使用较长路径和较大电容器以缓解信号反射。但DDR3布线情况不同,对线路长度和电容器数值敏感度更高。为确保信号完整性,DDR3需采用较短路径、较小电容器,并辅以阻抗匹配技术以降低反射。

3.时序控制的重要性

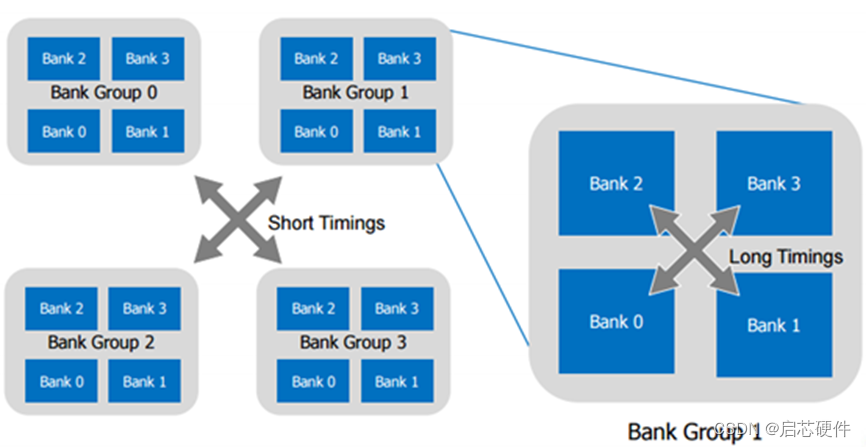

时序管理是DDR2及DDR3布线设计的关键要素。此过程涉及确保数据与时钟信号的协调同步。在DDR2和DDR3技术中,对数据与时钟时序的精准控制至关重要,以实现数据准确传递。

DDR2布线设计中的时序管理相对简便,得益于其较低的工作频率和较小的时钟与数据信号时序误差。反观DDR3,随着频率的提升,时序误差管理变得更加繁杂。设计者必须精确核算时钟与数据信号间的时序,并实施有效补偿策略,如应用延时线或修改走线长度,以维持时序精确性。

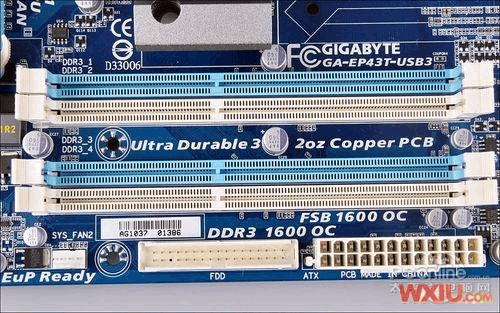

4.电源管理与功耗控制

在DDR2与DDR3的布线设计中,电源管理是一项关键考量。由于DDR3的电压需求低于DDR2,其电源设计需更为细致。该设计不仅需确保电源的稳定与噪声抑制,还需优化能耗表现。

DDR2布线阶段,电源管理着重于保障电源稳定与降低噪声干扰。设计师须保障电压电流的稳定性,并实施策略以减轻电源噪声对信号的干扰。至于DDR3布线,除稳定性和噪声控制外,功耗优化亦为关键。设计师可通过调节电源电压和电流,并实施低功耗设计技术,以降低系统总功耗。

5.布线布局与走线策略

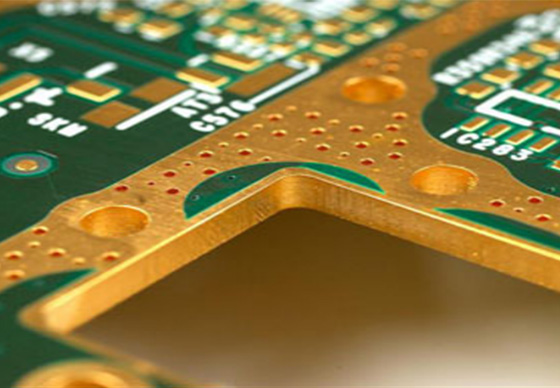

布线布局及走线方案构成DDR2与DDR3线路设计的关键要素。布线布局关注内存模块的物理排列及线路设计,而走线策略着重于走线长宽距等参数的优化。

在DDR2布线设计中,布局相对宽泛,允许按传输要求调整走线长度与宽度。相较之下,DDR3布线因高频信号对走线尺寸敏感,需进行更细致的布局与走线规划。设计师必须针对传输需求调整走线长度、宽度和间距,以维护信号完整性与时序精确性。

6.测试与验证方法

DDR2与DDR3布线设计的终极阶段为测试与验证,其为保障系统性能与稳定性的核心步骤。此过程包括信号完整性、时序性及电源等多个维度的测试。

DDR2的布线测试与核实流程相对简便,集中于确保信号完整与时序精度的达标。工程人员可借助示波器、逻辑分析仪等手段进行信号检测与核实。反观DDR3布线,测试与核实过程较为复杂,这源于高频信号的测试对设备和方法提出了更高要求。工程师需依托高精度测试设备,并采纳先进测试技术,以保障系统性能与稳定性。

7.未来发展趋势

随着计算机技术的持续进步,DDR2和DDR3布线技术亦同步升级。展望未来,伴随高性能与低能耗内存技术的发展,布线设计预计将遭遇更多挑战与机遇。

基于DDR2与DDR3的布线平台,未来设计将着力提升信号完整性、时序和电源管理之优化。设计师须不断更新并精通前沿布线技术与方法,以适应内存技术的演进之需。

结束语中,拟就设计领域中的信号完整性与时序控制问题于DDR2与DDR3布线处理方式向读者提问。敬请于评论区交流您的实用经验与观点。同时,诚挚邀请您点赞及转发文章,以推广DDR2及DDR3布线技术的关键性认知。