Quartus是一款在FPGA开发领域广泛应用的软件。DDR原语在它里面扮演着至关重要的角色。DDR原语能帮助我们高效地与DDR存储器进行交互,而这正是提升系统整体性能的关键所在。只要我们能够正确理解和运用Quartus中的DDR原语,开发过程就会变得更加顺畅和高效。

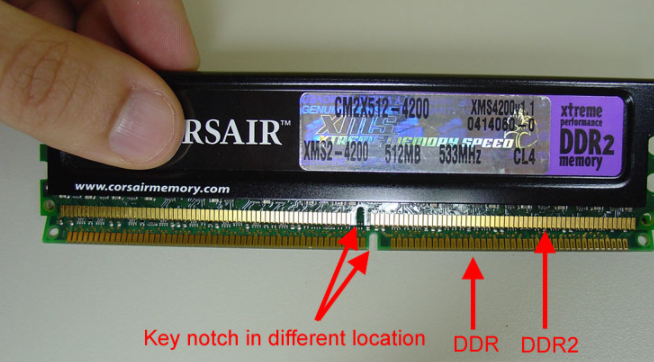

什么是DDR原语

DDR原语,这是专为DDR操作设定的基本单元。它是官方提供给开发者的便捷工具。在FPGA开发过程中,若没有DDR原语,操作DDR就必须从基础做起,那将是一项极为繁琐的任务。这就像盖房子,若没有现成的砖块,每块都要从挖土开始制作,岂不是麻烦透顶。Quartus的DDR原语能显著简化DDR操作流程,提升设计效率。它就像现成的组件,直接使用即可减少大量不必要的劳动。

DDR原语并非孤立存在,它与Quartus开发流程紧密相扣。融入整个流程后,DDR原语犹如链条上的重要一环。若忽视其存在或使用不当,就如同链条断裂一环,整个项目的开发进程将受到严重影响。

DDR原语的类型

Quartus支持多种DDR原语。例如,存在专门用于数据写入的原语,该原语能够满足将FPGA中的数据快速写入DDR存储器的需求。在高速数据采集系统中,当需要存储大量采集数据时,这种写入原语尤为有用。它能确保数据以极高的速度稳定地记录到DDR中。

有专门用于数据读取的指令。当我们需要从DDR中提取数据来处理或继续传输时,必须使用这些指令。比如在图像显示系统中,DDR里存储的图像数据必须被提取出来才能进行显示,这时读取指令就能精确且高效地完成这项任务。这两种指令相互协作,才能确保DDR操作流程的完整性。

如何使用DDR原语

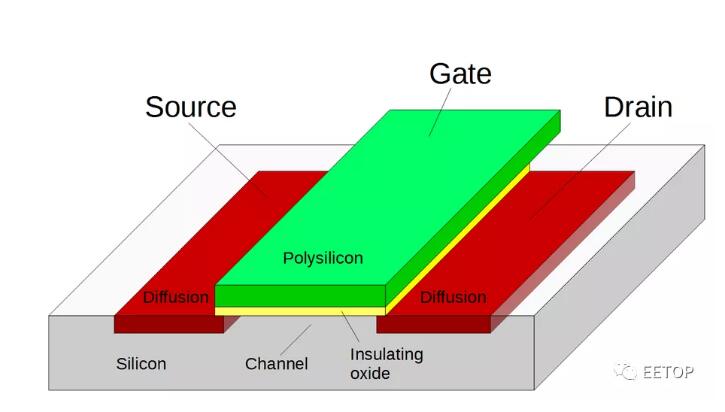

了解DDR原语的参数设置是首要任务。不同项目可能会有不同的需求,因此参数的调整是必要的。比如,数据的位宽和读写时序等参数都可能需要调整。操作过程中,可以参考Quartus的官方文档,那里有关于参数的详细介绍。

代码中的实例化环节紧随其后。必须准确地将DDR原语融入到自己的代码架构中。这并非易事,需要经过反复调试才能找到正确的实例化方法。一旦实例化出错,便可能引发数据读写失误,甚至导致系统崩溃。这就像组装机器时,若零件安装不当,机器便无法正常运行。

DDR原语的配置要点

时序配置对于DDR原语配置至关重要。DDR存储器对时序的要求极为严格,一旦时序配置不当,数据传输便可能出现错误。因此,在配置时序时,必须参照DDR存储器的手册,同时还要考虑整个系统的时钟频率等因素。

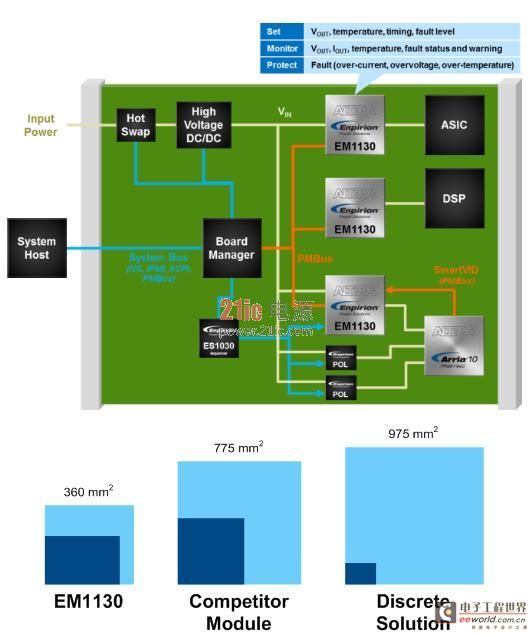

电源管理同样至关重要。恰当的电源管理对确保DDR原语及其关联的DDR存储器稳定运作至关重要。比如,调整至适宜的电压,以防止电压过高或过低对数据传输的稳定性造成影响。这直接影响到整个系统是否能够长时间稳定运行。

常见问题与解决

常见问题之一是数据读写出现了错误。遇到这种情况,我们首先要做的便是核对时序配置是否准确无误。若时序配置不当,就好比火车未按时刻表行驶,数据便会错送到错误的位置。

还有一个问题,就是DDR原语与其他模块间的兼容性问题。有时,DDR原语被引入后,会与现有的其他模块产生冲突。这时,我们必须重新审视模块之间的连接和交互逻辑。这就像调整两个人的协作方式,若配合不当,问题便会出现。

DDR原语的优化

从代码优化的角度来看,我们可以删减那些不必要的代码片段。这样做有助于提升DDR原语的执行速度。比如,我们可以移除一些多余的判断语句,从而使数据传输路径更加直接。

在硬件资源的使用上进行优化,通过合理分配硬件资源,DDR原语能够更高效地运作。例如,可以恰当地运用FPGA内部的存储块等资源,与DDR原语相辅相成。

最后我想请大家分享一下,在使用QuartusDDR原语的过程中,你们遇到了哪些特别棘手的问题?希望各位能点赞并转发这篇文章,也欢迎在评论区积极参与讨论。