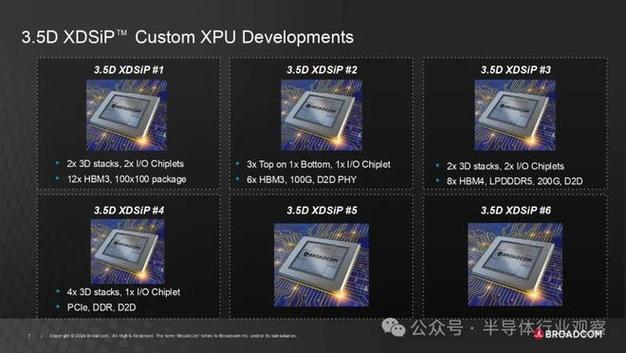

近期,科技界传来重大新闻,博通于12月8日推出全新3.5DXDSiP封装技术。该技术专为高性能AI和HPC处理器量身定制,预计将推动相关领域的创新与进步。

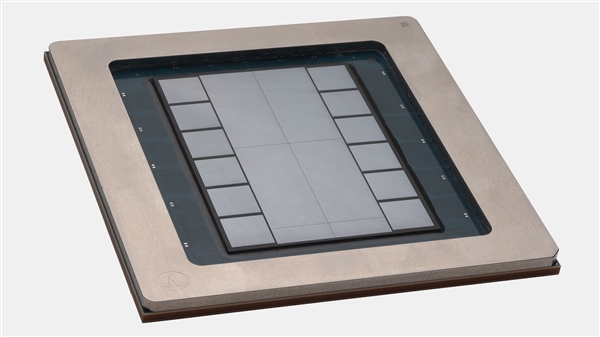

平台支持的芯片面积

该平台的最大芯片面积可达6000平方毫米,这一数据令人瞩目。以NVIDIABlackwell架构的后续旗舰芯片GB202为例,其面积仅为744平方毫米,而博通平台所支持的面积几乎相当于八颗GB202的总和。如此之大的面积支持,足以应对更复杂的芯片设计需求。这也反映出博通在芯片封装技术领域的雄心,致力于为大型、复杂的AI和HPC处理器提供合适的平台。此举不仅可能对博通自身业务带来影响,还可能对整个超高性能处理器行业产生深远变化。

这一芯片面积的支持能力,将如何具体地革新AI与HPC领域的处理任务?这是一个值得我们深入探讨的问题。

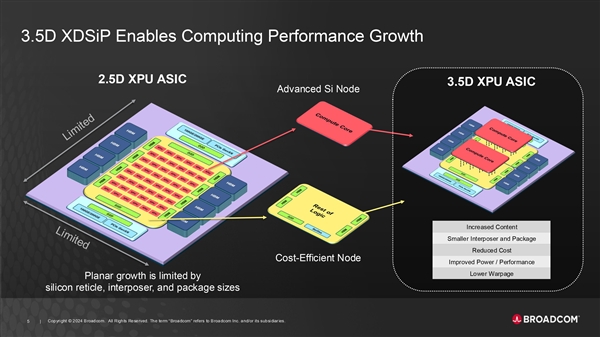

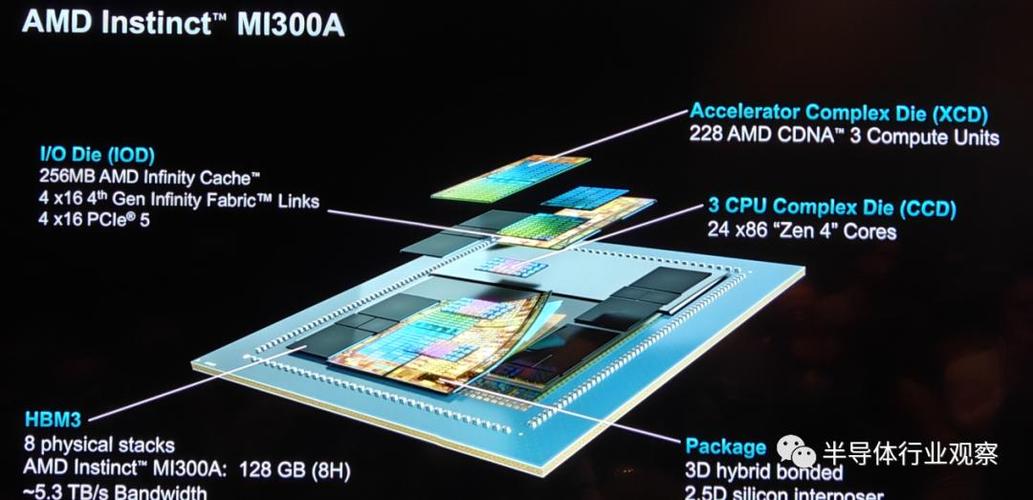

采用的封装技术

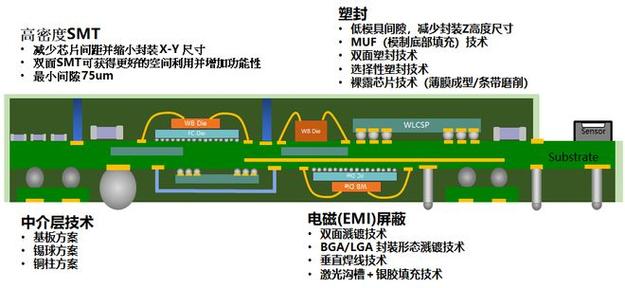

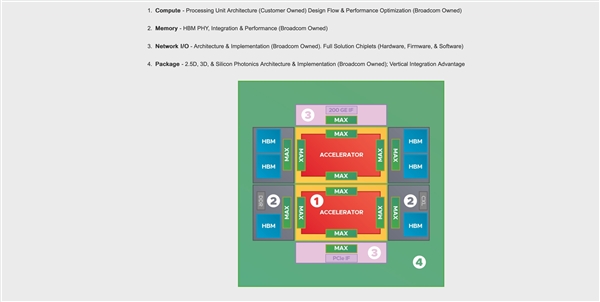

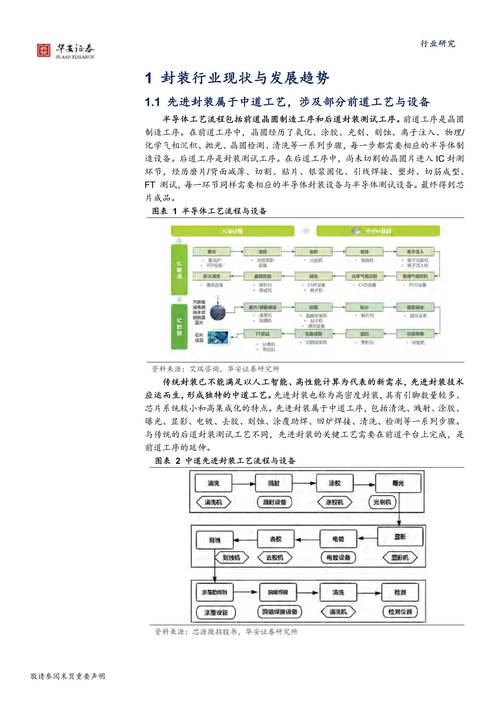

博通3.5DXDSiP采用了台积电的CoWoS-L封装技术,该技术结合了2.5D集成与3D封装技术,因此得名3.5D。此技术平台具备多种组件的整合能力。借助该技术,3D堆栈芯片、网络与I/O芯粒、HBM内存得以整合成系统级封装(SiP)。这种整合在芯片封装领域属先进技术,显著提升了芯片的整体性能和运行效率。

在众多芯片封装技术中,博通所采用的封装技术有何显著特点?这些特点如何使其在竞争激烈的市场环境中独树一帜?这是众多企业共同关注的问题。

中介层面积与内存芯片封装能力

该平台的顶级中介层面积高达4719平方毫米,这一数值约为光罩面积的5.5倍。此外,它具备卓越的内存芯片封装技术,能够封装多达12颗HBM3或HBM4高带宽内存芯片。这种封装技术显著提升了数据处理速度和整体性能。对于对内存性能有极高要求的AI和HPC处理器而言,博通推出的该平台无疑是一大优选。

博通平台的中介层面积及内存封装功能,是否会对其他同类封装平台造成影响?这一议题有必要进行深入研究。

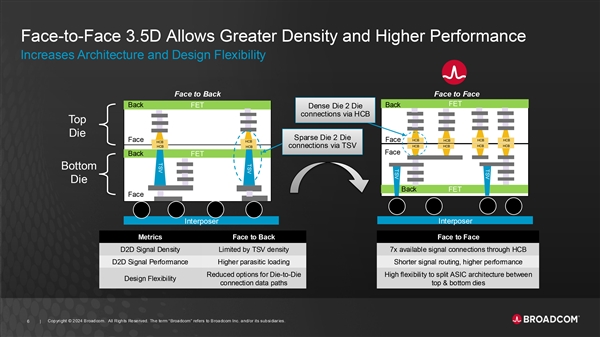

达成最高性能的方式

博通为追求极致性能,提出了一种新颖的设计理念。该理念倡导对计算单元进行独立设计,并利用混合铜键合技术(HCB),通过面对面(F2F)的方式将这些单元叠加。该技术的核心是采用无凸起HCB将上层芯片与底层芯片堆叠,摒弃了传统的硅通孔(TSV)技术。此举带来了显著优势,如信号连接数量提升约7倍,信号路径缩短,互连功耗最多降低90%,同时极大减少了延迟,并提高了堆叠的灵活性。

这种性能提升手段能否成为芯片堆叠的未来主流标准尚存疑问。验证其可行性需要经历时间的考验以及更多实际操作的检验。

面向客户的服务策略

博通计划采用3.5DXDSiP封装技术,为Google、Meta、OpenAI等公司量身打造AI/HPC处理器及ASIC芯片。此外,博通还将向这些客户提供包括HBMPHY、PCIe、GbE在内的多种IP资源,以及完整的芯粒方案和硅光子技术。此举旨在减轻客户负担,使他们能专注于处理器核心部分——处理单元架构的设计,无需担忧外围IP和封装事宜。这种服务模式在吸引高端客户方面具有显著优势。

博通所采取的服务策略,其能否吸引更多科技企业的合作,这一点值得关注。

产品推出时间

博通预计其首款产品将于2026年问世。这一推出计划引发了外界对新封装平台产品的浓厚兴趣与期待。在此期间,博通将持续改进其平台技术。同时,科技行业也将持续进步,竞争愈发剧烈。到了2026年,博通如何在不断演变的科技环境中稳固其产品地位,成为其必须思考的关键问题。

如对博通最新推出的平台感兴趣,请给予点赞、转发本篇文章,并欢迎在评论区分享您的观点。