笔者身为电子工程师,对DDR(双数据率)差分时钟电压颇感兴趣。原因在于,此电压不只于电子领域重要,更隐藏诸多奥妙。在此文中,笔者将引领您深度探究这一独特课题,涵盖基础理论与实际应用。

1.DDR差分时钟电压的基础概念

DDR差分时钟电压作为现代电子体系结构中的重要元素,主要负责驱动各类存储器及其它关键器件的时钟信号。在DDR这种双数据速率模式下,数据需在上升沿与下降沿同时传送,故为实现同等数据传输效率,该类技术须借助差分时钟信号。此信号由两路相位互为反相的波形构成,其压差便充当数据传输媒介,具备较高的抗干扰性以及高速传输性能。

在电路设计中,DDR差分时钟电压的稳定性及精确度至关重要,因其对整个系统性能与稳定产生直接影响。故需在设计阶段充分考量电源噪声以及信号完整性的影响,以保证时钟信号的优质与可靠。

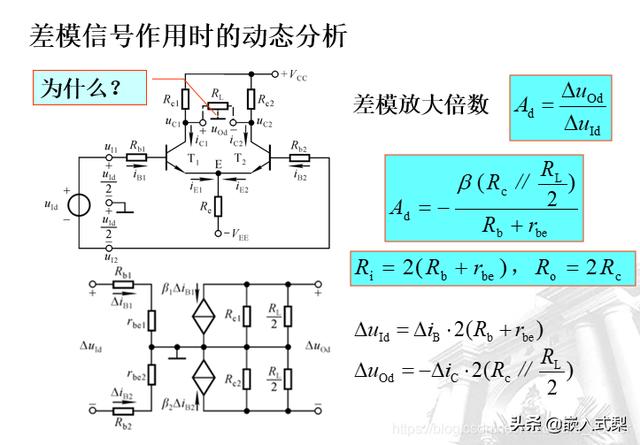

2.DDR差分时钟电压的工作原理

DDR差分时钟电压运作原理关乎多重因素,包括信息传输与电路构建等。在DDR存储技术中,时钟信号担任着协同数据读写的角色,以此确保数据能精确无误地存入存储器。而差分时钟信号,以相逆的两个信号传输数据,其中一个代表"0",另一个则代表"1",通过二者间的电压差异来体现数据。

在实践中,为确保DDR差分时钟电压的稳定性和精确度,严谨的电路设计与合理的布局显得尤为重要。如采取低噪电源设计、完善的接地网络等方法以降低电路中的干扰及噪声,进而提升时钟信号的品质与稳定性。

3.DDR差分时钟电压的重要性

DDR差分时钟电压在先进电子装置中的角色及影响不可小觑。首先,其性能与稳定性对系统的整体运行产生决定性影响。其次,DDR科技的革新也促进了电子产业的发展,推动关键元件如存储单元、处理器的改良。加之数据传输速度的持续提升,对时钟信号的稳定度和精确度提出更高要求,从而更凸显出DDR差分时钟电压的重要性。

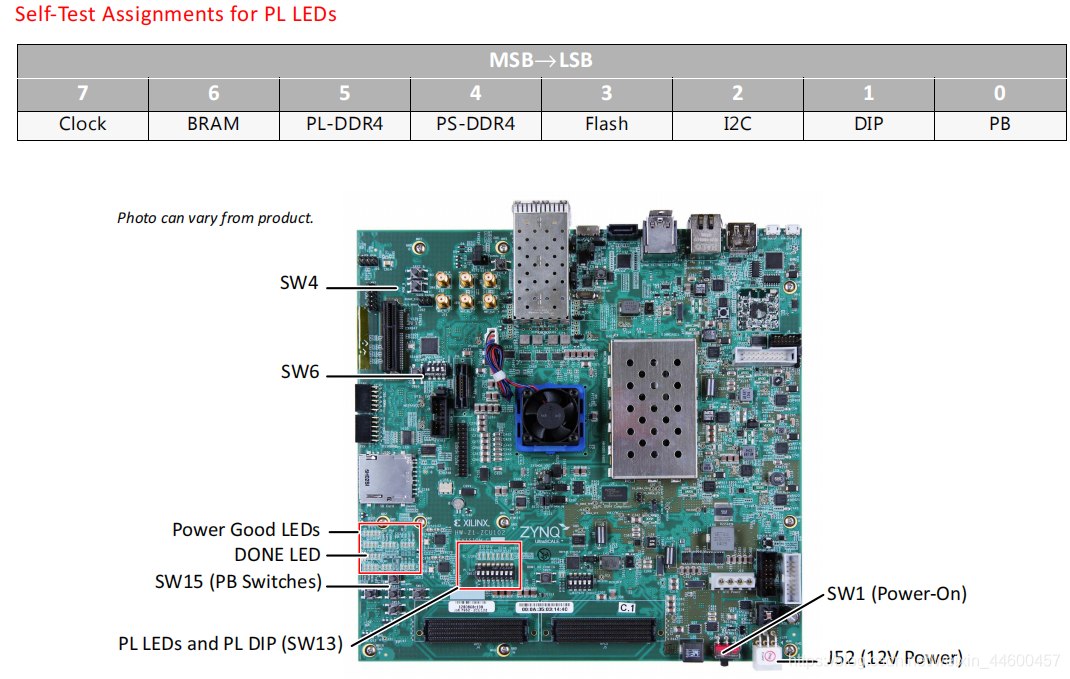

4.DDR差分时钟电压的应用实践

DDR差分时钟电压的实际运用,涵盖了电路构造与系统整合等多重环节。电路设计上,保证时钟信号品质稳定至关重要,可通过精细的电源设定及严谨的地线规划提升其抗扰性与传输速度。而在系统整合过程中,必须实施严谨的时钟信号测试与核实,确保达到既定的设计规范与标准,以此保障整个体系的正常运作及耐久性。

5.DDR差分时钟电压的未来发展

随着科技日新月异的进展,DDR差分时钟电压亦将直面新的挑战与机遇。展望未来,高速数据传输及电子系统日益复杂化,时钟信号的稳定性与精确度需求愈发严苛,势必驱动DDR技术持续革新与突破,引领电子产业蓬勃发展。

6.DDR差分时钟电压的挑战与应对

尽管DDR差分时钟在现今电路系统中占据重要地位,但同样面临挑战与困境。以当下的数据传输速度持续提升为例,时钟信号的抗干扰及传输能力需求亦随之攀升,这无疑对电路设计与布局提出了更高标准。此外,电子系统日趋复杂化,对时钟信号的稳定度与精确度构成了更大压力。面对这些问题,我们需借助尖端电路设计技术以及优化的系统集成策略等手段,以提升时钟信号的品质与稳定性。

7.结语

深度探究DDR差分时钟电压原理,让我们领略到该技术基础理论以及运作机制。同时,认识到了其在电子领域里举足轻重的地位及其实际运用实例。展望未来,DDR技术的发展趋势及所遇困境引发我们对创新与突破的思考,以此助力电子产业持续进步。