11月28日,台积电如期公布了超大版CoWoS封装技术的认证信息。该技术亮点纷呈,然而,同时也遭遇了不少挑战,值得业界关注。

技术核心亮点

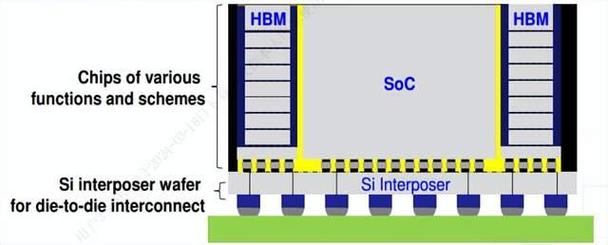

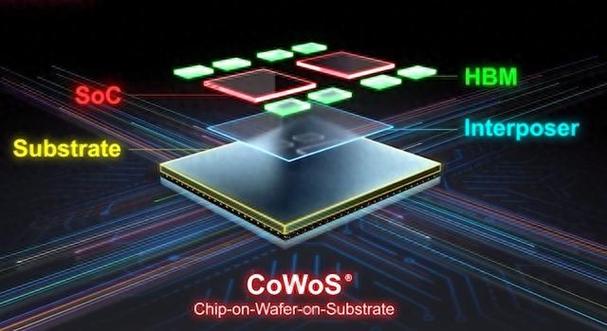

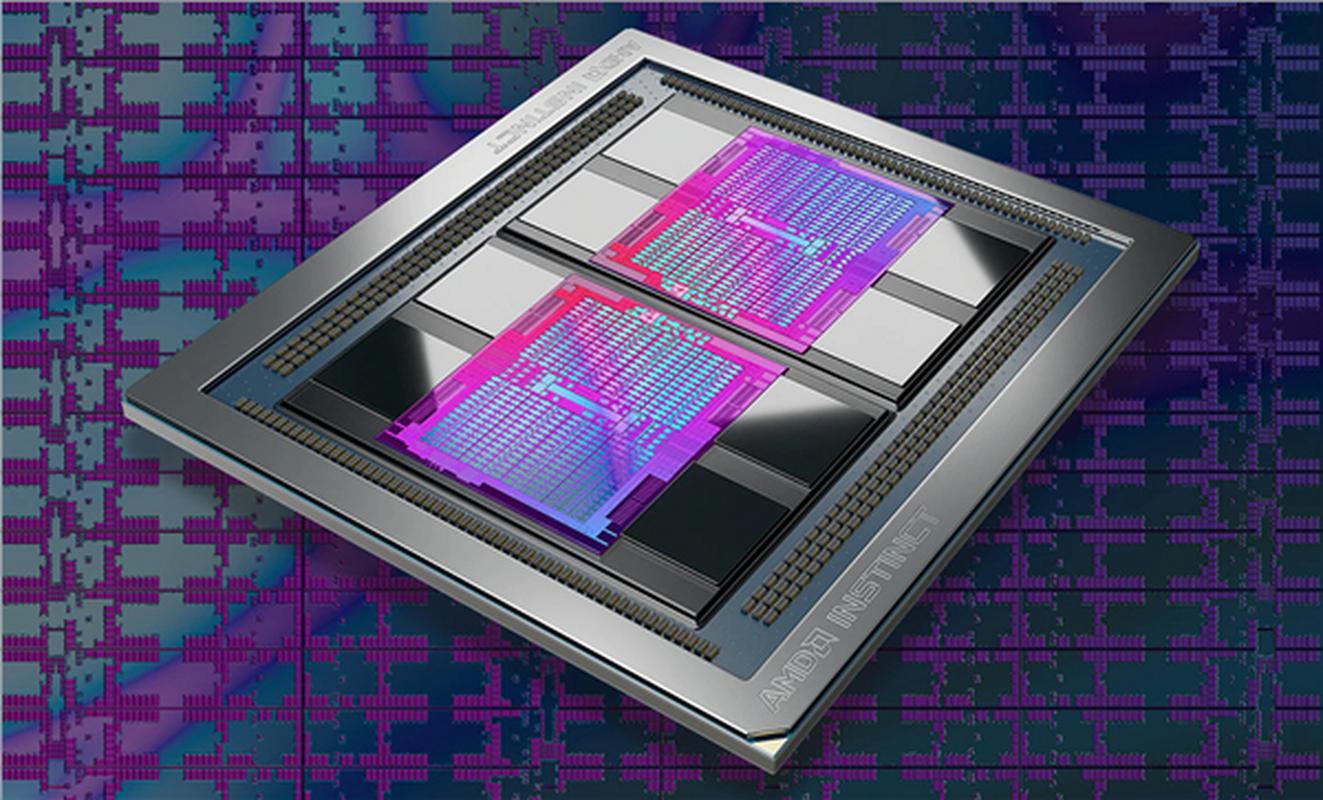

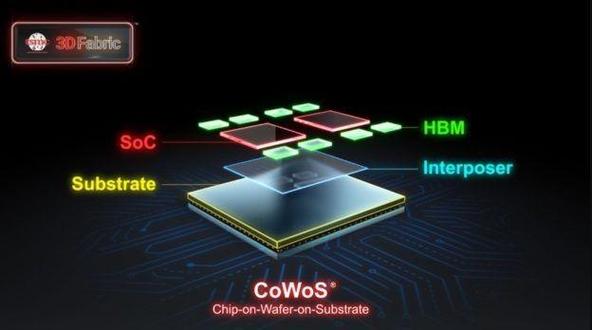

目前,台积电的CoWoS封装技术在11月28日的报道中被提及,其显著特点是能够容纳多达九种不同尺寸的光罩中介层。此外,该技术还集成了12个高效能的HBM4内存堆栈,专为高端性能需求设计。因此,对于追求高性能的设备或大规模计算环境,这项封装技术可能提供了更合适的解决方案。同时,从芯片性能提升的潜力来看,这种配置颇具吸引力。

据调查,此先进技术对未来芯片性能的提升具有正面影响。若应用于高端数据处理设备,将显著提高数据处理速度。此外,该技术能显著增强设备在高速数据传输及大规模运算方面的效率。

面临尺寸挑战

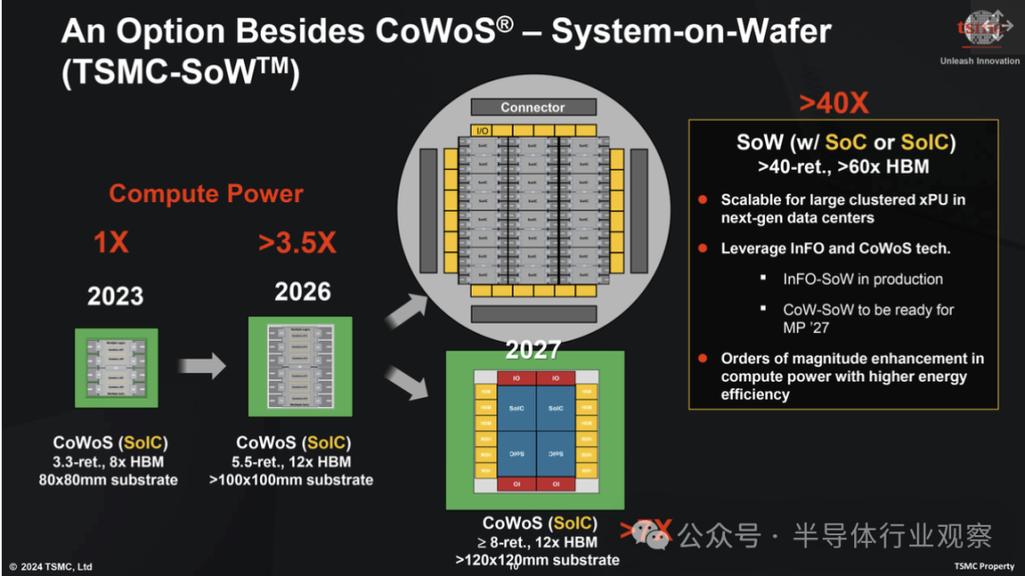

实现超大版CoWoS封装技术的理想效果颇具挑战。据悉,即便是最小5.5光罩尺寸的配置,也需基板面积超过100毫米乘以100毫米。此尺寸已接近OAM2.0标准尺寸的上限,即102毫米乘以165毫米。若追求9个光罩尺寸的极致,基板尺寸将超过120毫米乘以120毫米。这一目标无疑是一项重大挑战。

从实际生产制造层面分析,现有设备与该尺寸基板的需求可能存在不匹配问题。可能需研发新型设备或优化工艺流程。此举无疑会提升成本,并延长生产周期。

对系统设计影响

此类基板尺寸的变动,导致系统设计全局布局需作重大调整。当前多数系统设计参照既定的芯片封装规范,而尺寸的突变迫使数据中心在架构规划阶段必须重新规划电路板布局等相关事宜。

这也引发了与其他组件协同时的新挑战。例如,主板上的其他芯片与元件的布局需要重新评估。同时,如何确保这些元件与采用超大版CoWoS封装技术的芯片之间实现更优的互连,以保障系统稳定高效运作,成为了一个亟待解决的课题。

数据中心新要求

台积电的技术创新要求数据中心进行多方面调整。在电源管理领域,尺寸的调整可能引发电源使用模式的转变。若继续沿用旧有电源管理方案,芯片及系统性能可能无法充分发挥,甚至可能引发故障。

散热效率的提升同样至关重要。据11月28日公布的信息,芯片尺寸的调整将导致热量分布和总量的改变。若散热工作未能及时或均匀进行,将显著缩短芯片的使用寿命并影响其稳定性。

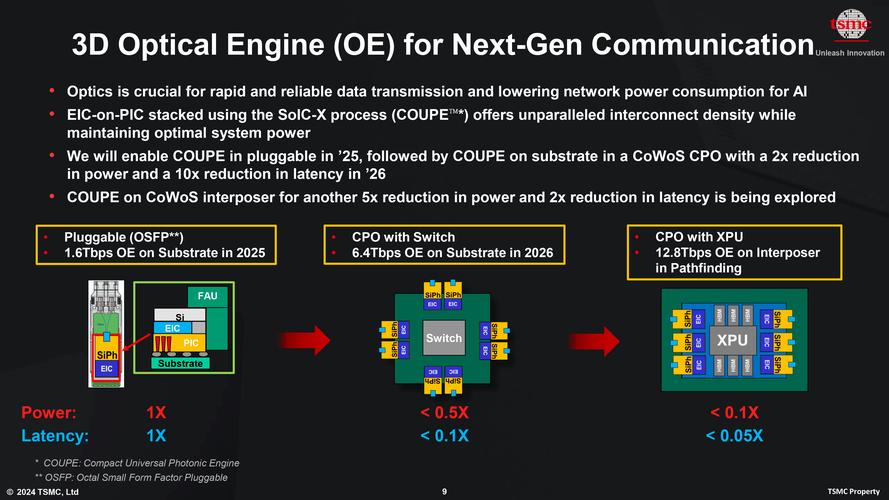

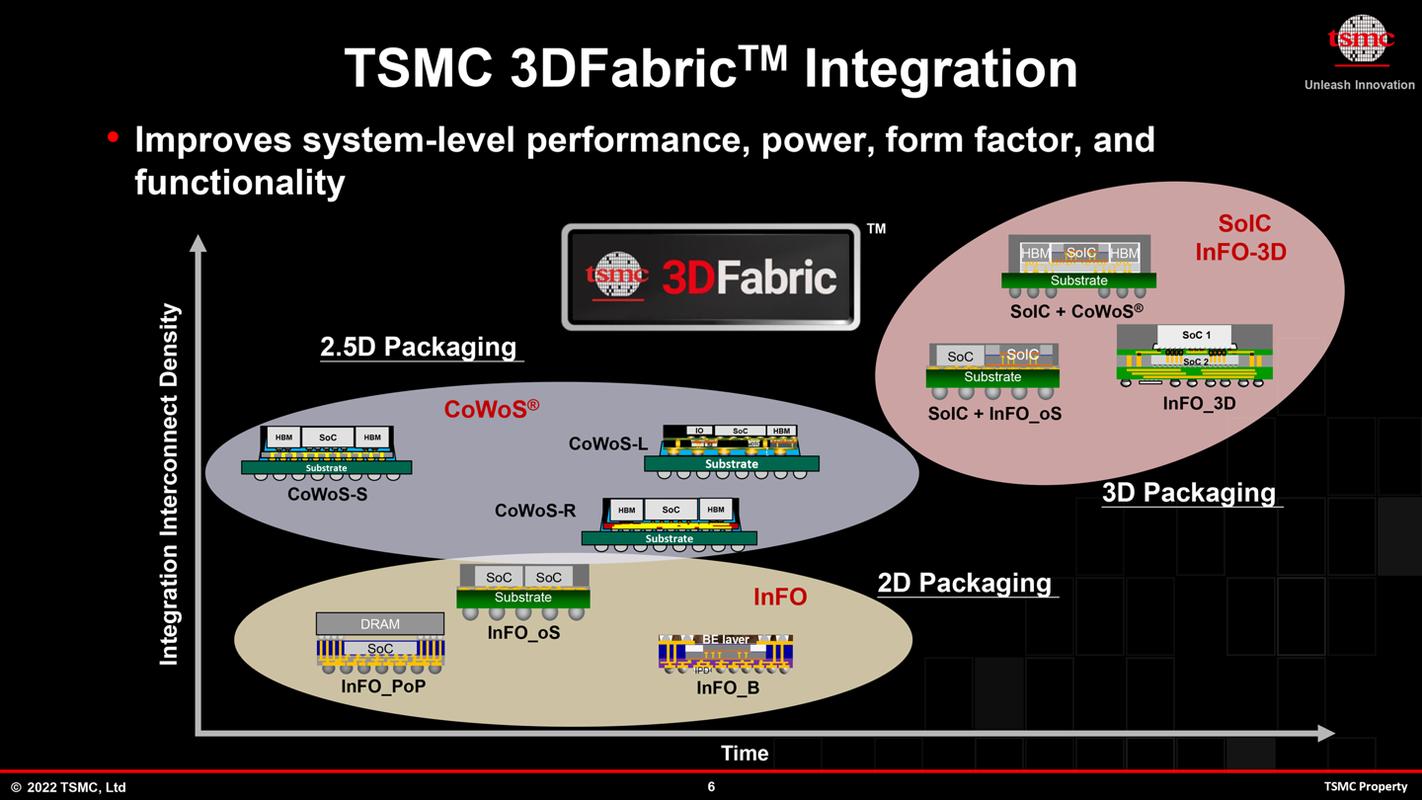

与SoIC技术结合

台积电期望采用其先进封装技术的企业能够运用SoIC技术实现逻辑芯片的垂直堆叠。此举对增加晶体管数量及提升性能有显著帮助。以CoWoS封装技术为例,该技术采用9个光罩尺寸,台积电预测客户将把1.6纳米芯片置于2纳米芯片之上。

这种结合有助于在更紧凑的物理空间中实现更多元件的集成。从技术发展的长远视角来看,这对提升芯片的集成度以及减小芯片的整体体积具有显著的正向影响。

未来展望

尽管挑战众多,台积电的CoWoS封装技术如若得以顺利实施,有望在芯片行业激起连锁反应。尽管现有资料表明前路坎坷,然而科技进步不正是源于对难题的攻克吗?

疑问随之产生,台积电是否能够成功实施其超大尺寸CoWoS封装技术?诚邀各位参与讨论,并期待大家对该文章给予点赞及转发。