当前,随着科技的迅猛进步,台积电的2纳米制程技术进展备受关注。新竹宝山工厂的试产启动,且其良率超出预期,这一喜讯既预示着科技进步的曙光,同时也引发了市场对于成本和价格可能攀升的忧虑。

台积电2nm试产概况

12月9日,快科技报道,台积电新竹宝山工厂已启动2nm工艺的试生产,良率高达60%,超出内部预期。此外,台积电计划在明年上半年于高雄工厂展开试产。对比其他如三星等芯片制造商,在推进制程技术时常遇挑战,台积电的试产成果彰显了其雄厚的技术能力。台积电的持续进步对全球芯片供应链的稳定至关重要,此次2nm试产使其在先进制程竞争中再度领跑。公司正计划逐步提高良率,达到大规模量产所需的70%以上,以确保后续生产顺利进行。

该进程的持续发展给合作企业带来了新的期待。目前,众多高科技公司,包括苹果在内,正依赖于台积电的尖端工艺。2纳米工艺的顺利试验生产,将助力这些公司未来推出更高效能的产品。

量产良率标准

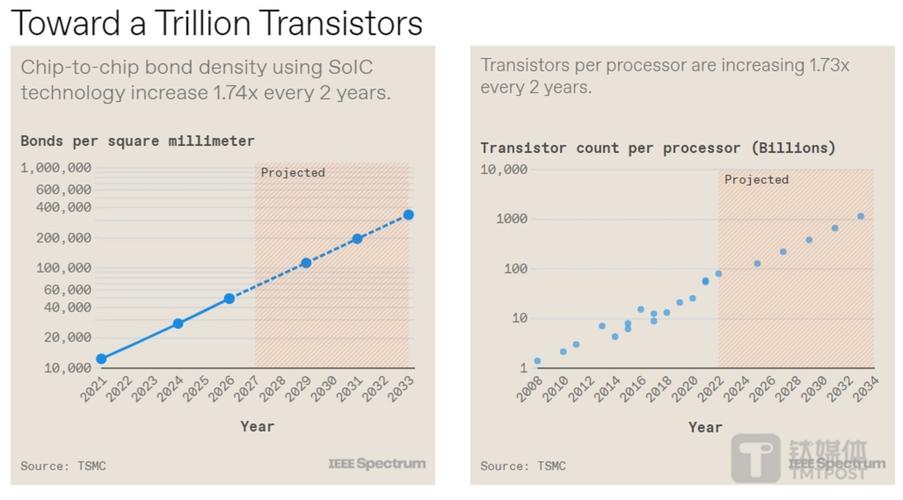

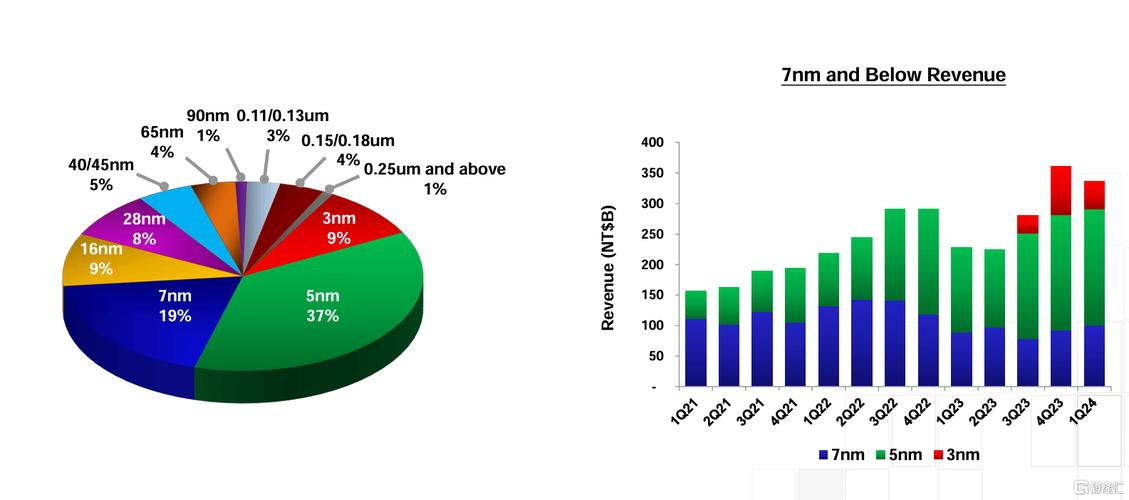

代工厂在批量生产芯片时,通常要求达到70%以上的良率。尽管台积电当前的良率只有60%,略低于量产标准,但根据现有进度,其仍有充足时间提升至所需水平。相比之下,部分小型代工厂在实现量产良率时可能遭遇技术和资金的双重挑战。然而,台积电凭借其深厚的经验和累积的技术,仍保持着领先地位。自2004年推出90nm芯片以来,台积电持续优化制程技术,从90nm发展到即将量产的2nm,技术成熟度显著提高。这一进步也为提升2nm芯片的量产良率提供了有力支持,台积电有望按既定计划完成大规模量产。

依据历史数据,台积电在从10纳米至5纳米制程的演进中,逐步解决了技术挑战,提高了产品良率。展望2纳米制程,公司有望延续这一进步态势。

2nm价格高涨

2nm制程技术的引入导致了成本的显著上升。据悉,台积电生产的2nm晶圆售价已超过3万美元,而3nm晶圆的当前价格介于1.85万至2万美元。与90nm制程时晶圆报价接近2000美元相比,可以看出技术进步越显著,价格上升越明显。在5nm制程阶段,晶圆价格已高达16000美元,并且这一价格尚未包含2023年6%的预期涨幅。

从企业财务角度来看,高昂的成本无疑会给芯片制造商带来经济负担。例如,高通和联发科在采用3纳米制程技术后,其终端产品价格普遍上涨。在2纳米制程阶段,这一问题可能加剧,由于成本更高,这或许会引起整个产业链的价格波动。

订单报价因素

台积电的订单价格并非恒定,它受到多方面因素的影响。比如,客户的具体情况和订单规模都会对价格产生影响。一些客户能够获得优惠,因此三万美元只是一个大致的估计。不同规模的芯片制造商在与台积电合作时,所面对的报价也会有所不同。小型的新兴芯片制造商可能需要支付接近三万美元的价格,而那些与台积电有大规模长期合作的客户则可能享受到折扣。这种报价方式不仅影响着客户的成本规划,还对整个芯片市场的合作与竞争格局产生了影响。

企业若打算采用2纳米制程技术,需综合考虑订单规模等关键因素,评估成本与收益,进而确立恰当的市场行动计划。

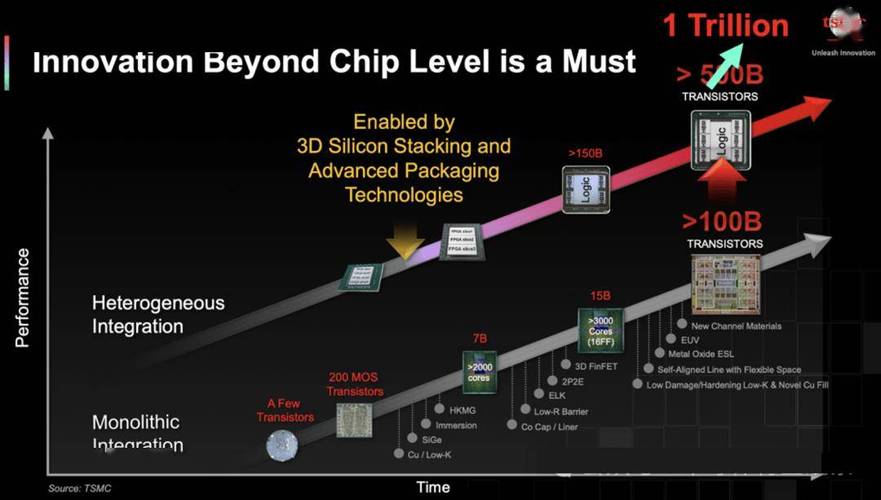

制程技术进步

台积电将在2nm制程阶段首次应用Gate-all-aroundFETs晶体管技术,并采用NanoFlex技术辅助。这一举措反映了台积电在技术革新领域的不断追求。相较于N3E工艺,N2工艺在性能和功耗等关键指标上显著进步,具体表现在相同功率下性能提升10%至15%,相同频率下功耗降低25%至30%,并且晶体管密度增加15%。

台积电的技术优势将增强其在全球芯片制造行业的竞争力。该技术能够提供性能更优、功耗更低的芯片解决方案,适用于消费电子产品等多个领域。例如,智能手机和电脑等产品将因此受益。

成本压力传导

2nm工艺的制造成本较高,导致芯片制造商面临较大成本压力,他们很可能会将这一压力转移。例如,高通和联发科之前因3nm工艺成本上升而提高了终端产品的售价。业界专家预测,在2nm工艺阶段,这种情况可能会更加严重。这可能导致下游客户或终端消费者面临更高的产品价格。对于消费者而言,购买高端手机等电子产品的费用可能会增加。这种成本传递效应范围广泛,不仅影响消费市场的热情,还可能对整个产业链的利益分配造成影响。

您如何看待当前芯片企业如何有效应对制程升级所引发的成本挑战?欢迎发表评论、点赞及转发本篇文章。