芯片代工领域迈入先进制程阶段,2nm技术节点成为行业竞争的关键点,无疑是当前行业关注的焦点。这一节点背后,涉及众多利益角逐、技术挑战,以及行业未来发展的不确定性。

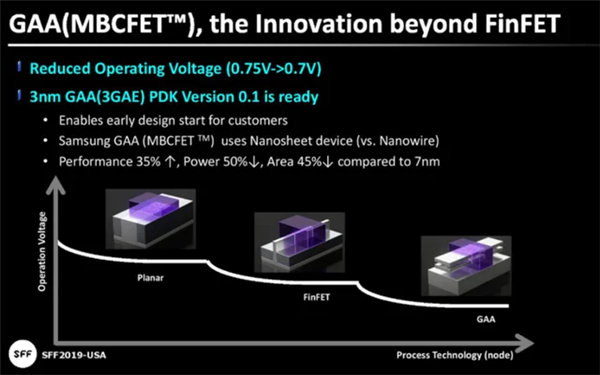

FinFET架构的兴衰

从技术视角分析,FinFET架构一度挽救了摩尔定律,延长了其生命力约20年。然而,随着芯片制程技术推进至5nm阶段,该架构开始显现出失效迹象。这一转变迫使芯片制造商在3nm及后续工艺节点上重新审视架构设计。在推进3nm工艺开发过程中,台积电持续优化FinFET结构。台积电技术实力显著,以苹果A17芯片为例,近两年采用其3nm代工的芯片在发热和功耗方面表现良好。此外,台积电3nm代工产线的良率超过80%,接近90%。

台积电的这一决策与其技术积累以及稳定生产的需求密切相关。鉴于消费电子产品对芯片稳定性要求极高的现状,这一举措无疑是一种谨慎而合理的策略。

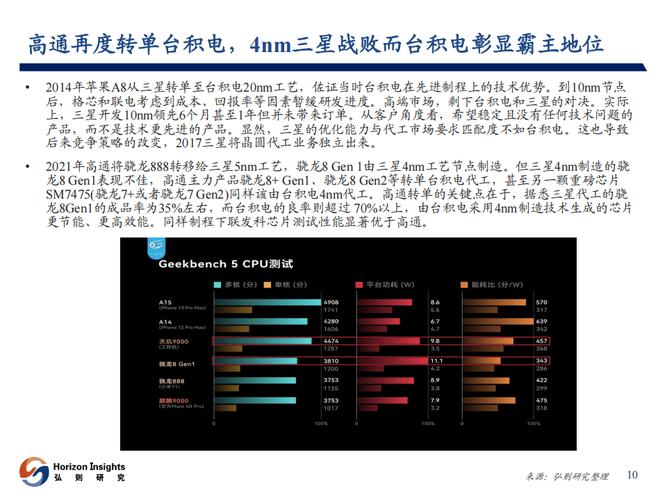

三星的激进策略

三星与台积电在3nm工艺节点上采取的策略大相径庭,前者直接采用了GAAFET架构。三星追求的是一步到位,但效果并未达到预期。这一情况也揭示了为何台积电在GAAFET架构试生产中即便遭遇三星的试产失败,仍能超出预期表现。在3nm工艺制程遭遇挫折后,三星计划在2nm工艺制程上奋起直追。有消息称,三星已暂停3nm工艺的研发,将全部精力投入到2nm工艺中。尽管三星华城的S3产线尚未开始量产3nm晶圆,却已着手准备将设备升级至2nm所需的配套设备,显示出其卷土重来的强烈决心。

三星此举旨在挑战现有的国际芯片代工市场布局。然而,过早引入新技术可能存在风险。技术从研发到成熟需经历一个阶段。三星在探索这一路径上的成功与否,尚待后续进展来揭晓。

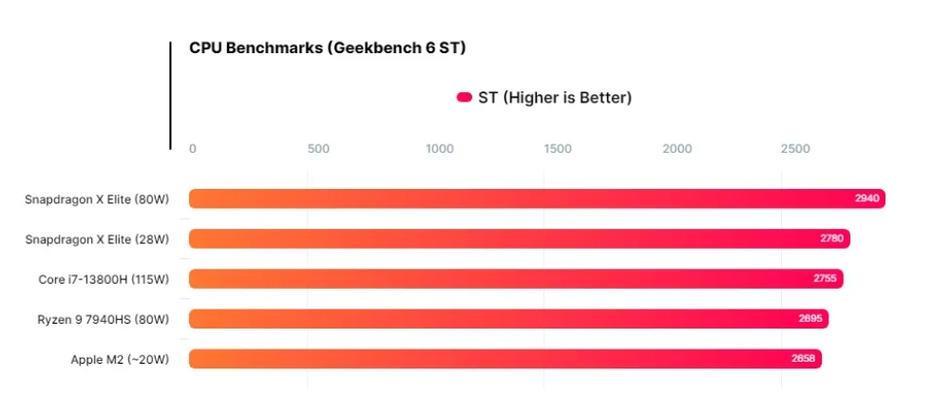

台积电2nm的功耗优势

台积电在架构更新方面较为谨慎,但在能耗控制方面保持领先。具体来说,N2制程的芯片在保持同等性能的前提下,能耗可降低至N3E的25%至30%。对于专注于SoC设计的消费电子芯片制造商来说,这种能耗优势尤为诱人。芯片能耗直接影响产品的续航能力等关键性能指标,在竞争激烈的消费电子领域,这一优势有望帮助台积电吸引更多客户。

较低的能耗可能促使产品在散热设计等领域的成本降低,同时也能增强用户的使用感受。此优势有助于台积电在市场上持续增强其地位。

2nm晶圆代工高昂价格

台积电的2nm制程晶圆代工费用预计将高达3万美元,4nm制程的代工费用约为1.5万美元,3nm制程的代工费用则达到1.85万美元。这种高价位主要源于生产成本的增加以及台积电在行业中的垄断地位。在今年,台积电已两次上调代工费用,不仅3nm制程价格上涨,连成熟的5nm制程价格也提升了4%至10%。这种价格上升给下游厂商带来了成本增加的挑战。

下游厂商面临抉择:是选择高价以保证产品性能与品质,还是寻找成本较低但可能存在不稳定的代工供应商。

英特尔的状况

英特尔已启动18A工艺(相当于2nm)的试生产阶段,然而,曝光显示其良率不理想,加之公司内部正经历变动,大规模生产尚无明确时间表。鉴于其在芯片领域的领先地位,英特尔当前状况可能导致其在2nm制程竞赛中处于不利位置。公司内部治理和技术向量产的过渡均需较长时间才能解决,短期内英特尔难以对台积电构成实质性挑战。

英特尔在芯片制造领域原本拥有丰富的技术积累,然而,面对当前的困境,这一事实无疑令人感到惋惜。

台积电一马当先

从整体情况分析,台积电在2纳米工艺技术的开发竞赛中明显占据优势。与此同时,三星与英特尔在技术上暂时难以与之抗衡。对于下游厂商而言,短期内面临台积电提价的现实。至于其他企业是否能够打破这一现状,目前尚无定论。未来,各大厂商如何应对台积电在2纳米制程方面的领先地位,将成为业界关注的焦点。

各位读者,关于2纳米制程技术的竞争,其他企业是否还有其他突破策略?我们期待您的观点、点赞以及对本文的传播。